# 28-nm CMOS 공정을 이용한 고속 첩 신호 합성기 설계

# Design of a Fast Chirp Frequency Synthesizer Using 28-nm CMOS Process

전영수 · 문준호\* · 박세준 · 신진욱 · 김병성

Young-su Jeon · Jun-ho Moon\* · Se-jun Park · Jin-uk Shin · Byung-sung Kim

유 약

본 논문에서는 28-nm CMOS 공정을 이용하여 고속 주파수 변조가 가능한 신호 합성기를 제시한다. 설계된 신호 합성 기는 이중 변조 기법을 도입하여 고주파 통과 영역과 저주파 통과 영역을 나누어 주파수를 고정한다. 고주파 통과 영역 에서 전하 디지털-아날로그 변환기(QDAC)를 이용하여 연속적인 주파수 변화가 가능하도록 설계하였다. 저주파 통과 영 역에서는 분주기와 델타-시그마 변조기를 통해 원하는 주파수에 고정할 수 있도록 설계하였다. 제작된 신호 발생기는 14.1 GHz∼16.2 GHz까지 주파수 고정이 가능하고, 1 MHz 오프셋 주파수의 위상잡음은 −100.14 dBc/Hz를 가진다. FMCW용 첩 신호 발생의 경우 42.8 μs 첩 타임과 860 MHz의 대역폭을 가진다. 전체 회로 사이즈는 1,070×700 μm²이다.

#### Abstract

This study proposes a frequency synthesizer with fast frequency modulation using a 28-nm CMOS process. The synthesizer used a two-point modulation technique that divides the frequency range into high- and low-pass regions to lock the frequency. In the high-pass region, continuous frequency modulation was achieved using a charge-digital-to-analog converter, while in the low-pass region, the synthesizer was set to the desired frequency using a divider and a delta-sigma modulator. The manufactured signal generator is capable of oscillating at frequencies between 14.1 GHz and 16.2 GHz, with a phase noise of -100.14 dBc/Hz at 1 MHz offset frequency. For chip signal generation, the generator had a chip time of 42.8 s and a bandwidth of 860 MHz. The chip area was  $1,070 \times 700 \ \mu \,\mathrm{m}^2$ .

Key words: LL, QDAC, TPM, Chirp, VCO

# Ⅰ. 서 론

최근 FMCW(frequency modualted continuous wave) 레이 다가 자율주행, 생체신호 탐지, 모션 인식 등 다양한 분야

에 사용됨에 따라 FMCW 신호 발생기에 대한 연구도 활 발해지고 있다<sup>[1]</sup>. FMCW 레이다의 첩 신호는 주파수가 시간에 따라 연속적으로 변조되며 송신된 신호와 수신된 주파수와의 차이를 통해 목표물의 거리, 속도 정보를 알

<sup>「</sup>본 연구는 IDEC에서 EDA Tool을 지원받아 수행하였습니다.」

<sup>「</sup>본 연구는 삼성전자의 지원(과제번호IO201209-07913-01)을 받아 수행된 결과임.」

성균관대학교 전자전기컴퓨터공학과(Department of Electrical and Computer Engineering, Sungkyunkwan University)

<sup>\*</sup>한화시스템(Hanwha Systems)

<sup>·</sup> Manuscript received March 16, 2023; Revised March 30, 2023; Accepted April 10, 2023. (ID No. 20230316-024)

<sup>·</sup> Corresponding Author: Byung-sung Kim (e-mail: bskimice@skku.edu)

수 있다. 최근 자동차용 FMCW 레이다는 속도 정보를 정 확하게 측정하기 위해 고속 주파수 변조를 사용하는 것 이 일반적이다. 하지만 일반적인 PLL은 피드백 루프의 대역폭이 제한되어 고속 첩 생성의 어려움이 존재한다<sup>[2]</sup>. 기존 PLL의 한계점을 극복하기 위해 사용하는 기법으로 직접적으로 VCO의 주파수를 설정하는 주입 경로와 피드 백으로 주파수를 고정하는 피드백 경로를 동시에 사용하 는 이중 변조 기법 TPM(two point modulation)이 널리 사 용되고 있다. TPM을 사용하는 최근 연구 중 참고문헌 [1] 은 ODAC와 서브샘플링 기법을 사용하여 매우 우수한 성 능을 보여주었는데, 이 방법은 서브 샘플링 기법상 부가 적인 주파수 고정 루프를 필요로 한다. 본 논문에서는 QDAC를 사용하는 주입 경로와 분주기를 사용하는 분수 형 PLL을 사용하는 이중 변조 기법을 제안하고 검증한 결과를 제시한다. Ⅱ장에서 제안하는 PLL의 설계를 설명 하고, Ⅲ장에서는 측정 결과, Ⅳ장에서는 결론을 제시한다.

### Ⅱ. PLL 설계

#### 2-1 PLL 전체 구조

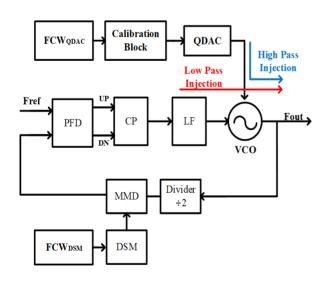

그림 1은 제안하는 이중 변조 기법을 도입한 PLL 전체 구조를 나타낸 것이다. 전체 PLL은 전하 디지털-아날로

그림 1. 제안하는 PLL 블록 다이어그램 Fig. 1. Proposed PLL block diagram.

그 변환기(charge digital to analog converter, QDAC), 전압 제어 발진기(voltage-controled oscillator, VCO), 분주기 (multi modulus divider, MMD), 델타-시그마 변조기(deltasigna modulator, DSM), 주파수-위상 검출기(frequencyphase detector, PFD), 전하 펌프(charge-pump, CP), 루프 필터(loop filter, LF)로 구성되어 있다.

PLL은 VCO가 고정된 주파수를 안정적으로 생성할 수 있도록 하는 회로이다. VCO에서 발생한 신호는 분주기에 의해 분주되어 PFD로 인가된다. PFD에서 기준 신호와 분주된 신호의 비교를 통해 위상 차이를 UP 또는 DN에서 필스 신호로 출력하게 된다. 이 두 신호는 전하 펌프에서 전류를 흐르게 하며, 전류에 따라 루프 필터에서 전압이 변하게 된다. 이러한 전압 변화가 VCO에 입력되어 주파수를 변조하게 된다. 시간이 지나면 VCO는 한 주파수에 대해 고정된 신호를 발생하게 된다.

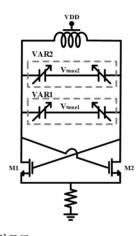

### 2-2 전압 제어 발진기(VCO)

VCO는 입력받는 전압값에 따라 출력되는 주파수가 바뀌는 회로로 PLL에서 가장 중요한 역할을 한다. VCO 설계 시 고려해야 할 특성은 위상 잡음, 주파수 이득, 전력소모 그리고 주파수 변조 범위 등이 있다. 본 연구에서는 상대적으로 넓은 주파수 변조 범위를 가지도록 VCO를설계하였다.

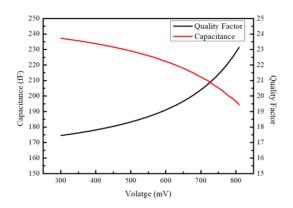

VCO의 발진 주파수는 식 (1)처럼 인덕터와 바랙터의 커패시턴스값으로 결정된다. 넓은 주파수 변조 범위를 가지기 위해선 큰 사이즈의 바랙터가 필요하다. 바랙터의 품질계수(Q)를 유지하면서 큰 사이즈를 가지기 위해 작은 사이즈의 바랙터를 병렬로 연결하여 큰 사이즈의 바랙터를 구현하였다. 그림 2는 바랙터의 15 GHz에서 전압에 따른 커패시턴스와 품질계수를 시뮬레이션한 결과이다. 0.3 V에서 커패시턴스는 237 fF과 17의 품질계수를 가지고, 0.8 V에서 커패시턴스는 195 fF과 23의 품질계수를 가진다. 그림 3은 VCO의 회로도를 나타낸다. VCO의 발진 주파수는 시뮬레이션상에서 14.8 GHz~16.3 GHz가 되도록 설계하였다.

$$f_{VCO} = \frac{1}{2\pi\sqrt{L_{id}C_{var}}} \tag{1}$$

그림 2. 전압에 따른 바렉터 시뮬레이션

Fig. 2. Simulation of varactor depending on voltage.

그림 3. VCO 회로도 Fig. 3. Schematic of VCO.

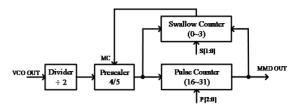

## 2-3 분주기(MMD) 및 델타-시그마 변조기(DSM)

분주기는 그림 4와 같이 VCO의 출력 주파수를 받아디지털 입력에 따라 128~254까지 분주가 가능하다. Swallow counter에 들어오는 입력에 따라 prescaler의 분주비가 4혹은 5로 바뀌게 되고, pulse counter는 디지털 입력에 따라 16~31까지 분주가 가능하도록 설계하였다. VCO의 출력을 받는 divider는 TSPC 구조를 사용하여 높은 주파수에서 동작할 수 있도록 설계하였다. 델타-시그마 변조기는 분수비를 입력으로 받아 정수의 평균값으로 분수비를 표현한다. 분주기의 디지털 입력을 변화시켜 원하는 주파수를 고정할 수 있도록 한다. 본 논문에서는 mesh 1-1 구조의 2차 변조기를 사용하였다.

그림 4. 분주기 블록 다이어그램

Fig. 4. Multi-modulus divider block diagram.

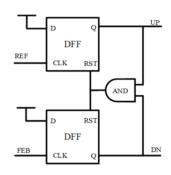

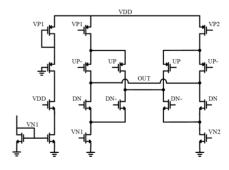

## 2-4 주파수-위상 검출기(PFD) 및 전하 펌프(CP)

PFD는 그림 5와 같이 2개의 DFF와 AND 게이트로 구성되어 있다. 기준 주파수 REF와 분주기의 출력 신호인 FEB를 입력받아 두 신호의 위상 차이에 비례하는 UP, DN 신호를 출력한다. CP는 PFD에서 출력되는 신호를 받아 전류를 조절하여 루프 필터에 전하를 충·방전시켜준다. CP의 전류의 크기는 UP 신호와 DN 신호에서 같은 전류가 흐를 수 있도록 설계하였다. 그림 6에서 VP1과 VN2,

그림 5. 주파수-위상 검출기 블록 다이어그램 Fig. 5. Frequency-phase detector block diagram.

그림 6. 전하 펌프 회로도

Fig. 6. Schematic of charge pump.

VP2와 VN1에 연산증폭기를 이용하여 VN1에 흐르는 전류와 VN2에 흐르는 전류의 크기가 같도록 설계하였다.

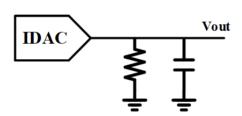

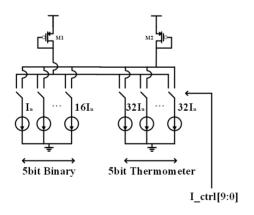

### 2-5 전하 디지털-아날로그 변조기(QDAC)

QDAC는 그림 7과 같이 IDAC의 출력단에 캡과 저항을 달아 기존에 VDAC에서 발생하는 이산 전압 변화 대신 연속 전압 변화가 가능하여 이산 전압 변화 시 바랙터에 발생하는 주파수의 공백이 없도록 설계하였다. 바랙터의 비선형성과 PVT(process voltage temperature)에 의한 비선 형성을 보정하기 위해 보정 회로를 설계하였다. 그림 8은 보정 회로의 회로도를 나타낸 것이다. 보정 회로는 10 비트로 구성되어 있으며, 첩 시간을 32개 구간으로 나누어 각 구간마다 계수를 512로 설정하고, 첩 하는 동안 발생하는 주파수 부정합을 보상하기 위해 계수 값이 바뀌게 되어 주파수가 선형적으로 변조할 수 있도록 설계하였다<sup>[1]</sup>.

그림 7. 전하 디지털-아날로그 변환기 블록 다이어그램 Fig. 7. Charge digital to analog converter block diagram.

그림 8. 전하 디지털-아날로그 변환기 보정 회로 회로도 Fig. 8. Schematic of charge digital to analog converter calibration circuit.

### 2-6 루프 필터(Loop Filter, LF)

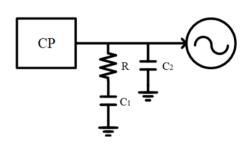

루프 필터의 대역폭은 PLL에서 전체 특성에 영향을 끼친다. 필터의 저항과 커패시터의 크기는 PLL 회로의 다양한 계수값에 영향을 받는다. 본 연구에서는 2차 RC 필터를 사용하여 0.2 MHz의 루프 대역폭과  $56^\circ$ 의 위상 마진을 가지도록 그림 9와 같이 설계하였다.  $C_1$ 은 9 pF,  $C_2$ 는 0.8 pF, R은 35 k $\Omega$ 을 가진다.

## Ⅲ. PLL 측정 결과

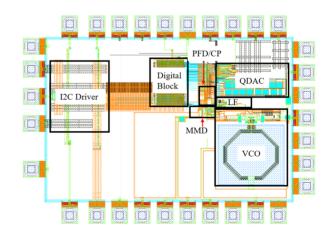

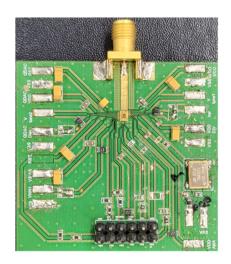

설계된 PLL은 PCB 보드를 이용하여 측정하였다. 그림 10은 설계된 PLL layout이며, PCB를 제작하여 측정하였다. 디지털 블록에 입력의 경우 MCU와 I2C Driver를 통해 코드를 인가하였다. VCO의 출력은 Keysight사의 N9030A 스펙트럼 분석기를 사용하여 측정하였다. 그림

그림 9. 루프 필터 블록 다이어그램

Fig. 9. Loop filter block diagram.

그림 10. 전체 PLL layout(1,070 μm×700 μm)

Fig. 10. Layout of PLL.

11은 PLL 측정을 위해 제작한 PCB이다.

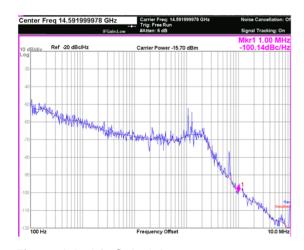

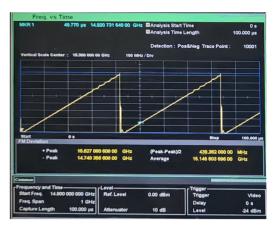

VCO의 발진 주파수는 전압에 따라  $14.1~{\rm GHz}\sim16.2~{\rm GHz}$  발진하였고, 그림 12는  $14.592~{\rm GHz}$ 에 고정하여 위상 잡음을 측정하였다. 오프셋 주파수는  $1~{\rm MHz}$ 로 설정하여 위상 잡음은  $-100.14~{\rm dBc/Hz}$ 가 측정되었다. 그림 13은 Anritsu사의 MS2850A 스펙트럼 분석기를 사용하여 첩 타임을  $42.8~{\mu}$ s로 설정하고, 첩 대역폭은  $860~{\rm MHz}$ 로 설정하여 측정하였다. 표 1은 PLL 성능을 비교한 표이다.

그림 11. 측정을 위한 PCB 보드

Fig. 11. PCB board for measurement.

그림 12. 위상 잡음 측정 결과

Fig. 12. Measurement of phase noise.

그림 13. 첩 측정결과

Fig. 13. Chirp measurement.

# Ⅳ. 결 론

본 논문은 28-nm CMOS 공정을 사용하여 이중 변조 기 법을 도입하여 고속 첩이 가능한 PLL을 설계한 결과를 제시하였다. 설계한 PLL은 14.1 GHz~16.2 GHz까지 주파 수 고정이 가능하고, 14.592 GHz에서 1 MHz의 오프셋 주 파수의 위상 잡음은 -100.14 dBc/Hz로 측정되었다. FMCW 신호 발생 시 첩 타임은 42.8 μs, 주파수는 14.8 GHz~15.6 GHz까지 사용 가능하다. 전체 전력 소모는 37 mW를 소모한다. 측정 결과, 첩의 끝부분에서 주파수가 흔들리는 형태가 보이는데, 이는 바랙터의  $K_{VCO}$ 가 큰 부 분에서 QDAC의 보정 회로로 인해 전압의 변화에 따라 민감하게 변조되는 것으로 추측된다. 추후 QDAC의 보정 회로의 구간을 32개 이상으로 증가시켜 선형성을 개선하 고자 한다. 또한 DTC(digital to time converter) 회로를 추 가하여 DSM에서 발생하는 양자화 잡음을 줄이고자 한 다. 이러한 점을 개선시킨다면 FMCW 레이다 시스템의 국부신호로 사용 가능할 것으로 예상한다.

#### References

[1] P. T. Renukaswamy, N. Markulic, P. Wambacq, and J. Craninckx, "A 12-mW 10-GHz FMCW PLL based on an integrating DAC with 28-kHz RMS-frequency-error for 23-MHz/μs slope and 1.2-GHz chirp-bandwidth," *IEEE*

| Ħ - | 1 의사    | 고저                                       | 루프의 | 서느    | () () | 미 | 비교 |

|-----|---------|------------------------------------------|-----|-------|-------|---|----|

|     | 1. TI & | ان تــــــــــــــــــــــــــــــــــــ | 1   | - A A | 끄 ㄱ   | ズ |    |

Table 1. Performance summary and comparisons of PLL.

|                                 | This work  | Ref. [1]   | Ref. [3]   | Ref. [4]   | Ref. [5]   | Ref. [6]   | Ref. [7]   |

|---------------------------------|------------|------------|------------|------------|------------|------------|------------|

| Architecture                    | TPM/Frac-N | QDAC/TPM/  | VDAC/TPM/  | TPM/Frac-N | DCO/TPM/   | QDAC/SPM/  | DCO/TPM/   |

| Architecture                    | PLL        | SSPLL      | SSPLL      | PLL        | BBPLL      | ADPLL      | ADPLL      |

| Reference frequency [MHz]       | 100        | 80         | 80         | -          | 52         | 26         | 40         |

| VCO frequency range<br>[GHz]    | 14.1~16.4  | 8.3~11.7   | 14.7~17.2  | 19~20.25   | 20.4~24.6  | 82.1~83.8  | 56.4~63.4  |

| Chirp bandwidth [GHz]           | 0.86       | 1.21       | 1.5        | 1          | 0.208      | 1.505      | 1          |

| Chirp+Idle time [us]            | 42.8       | 12.8       | 30         | 40         | 1.2        | 2000       | 210        |

| Chirp slope [MHz/us]            | 20.1       | 94.5       | 50.0       | 25.0       | 173.3      | 0.8        | 4.8        |

| fBW, PLL [MHz]                  | 0.2        | 3          | 0.1        | 0.3        | 0.2        | -          | 0.3        |

| Phase noise @ 1 MHz<br>[dBc/Hz] | -100.14    | -109.1     | -110.8     | -112       | -108.2     | -102.8     | -106       |

| Chirp waveform                  | Sawtooth   | Sawtooth   | Sawtooth   | Sawtooth   | Sawtooth   | Triangular | Triangular |

| Power [mW]                      | 37         | 11.7       | 44         | -          | 19.7       | 152        | 48         |

| Technology                      | 28 nm CMOS | 28 nm CMOS | 28 nm CMOS | 45 nm CMOS | 65 nm CMOS | 65 nm CMOS | 65 nm CMOS |

- Journal of Solid-State Circuits, vol. 55, no. 12, pp. 3294-3307, Dec. 2020.

- [2] J. W. M. Rogers, C. Plett, and F. Dai, *Integrated Circuit Design for High-Speed Frequency Synthesis*, Norwood, MA, Artech House, 2006.

- [3] Q. Shi, K. Bunsen, N. Markulic, and J. Craninckx, "A self-calibrated 16-GHz subsampling-PLL-based fast-chirp FMCW modulator with 1.5-GHz bandwidth," *IEEE Jour*nal of Solid-State Circuits, vol. 54, no. 12, pp. 3503-3512, Dec. 2019.

- [4] B. P. Ginsburg, K. Subburaj, S. Samala, K. Ramasubramanian, J. Singh, and S. Bhatara et al., "A multimode 76-to-81 GHz automotive radar transceiver with autonomous monitoring," in 2018 IEEE International Solid -State Circuits Conference-(ISSCC), San Francisco, CA, Feb. 2018, pp. 158-160.

- [5] D. Cherniak, L. Grimaldi, L. Bertulessi, R. Nonis, C.

- Samori, and S. Levantino, "A 23-GHz low-phase-noise digital bang-bang PLL for fast triangular and sawtooth chirp modulation," *IEEE Journal of Solid-State Circuits*, vol. 53, no. 12, pp. 3565-3575, Dec. 2018.

- [6] H. Sakurai, Y. Kobayashi, T. Mitomo, O. Watanabe, and S. Otaka, "A 1.5GHz-modulation-range 10ms-modulationperiod 180kHzrms-frequency-error 26 MHz-reference mixedmode FMCW synthesizer for mm-wave radar application," in 2011 IEEE International Solid-State Circuits Conference, San Francisco, CA, Feb. 2011, pp. 292-294.

- [7] W. Wu, C. W. Yao, K. Godbole, R. Ni, R. Y. Chiang, and Y. Han, et al., "A 28-nm 75-fs<sub>rms</sub> analog fractional-N sampling PLL with a highly linear DTC incorporating background DTC gain calibration and reference clock duty cycle correction," *IEEE Journal of Solid-State Circuits*, vol. 54, no. 5, pp. 1254-1265, May 2019.

### 전 영 수 [성균관대학교/석사과정]

#### https://orcid.org/0009-0001-8780-1139

2020년 8월: 인하대학교 전자공학과 (공학 사)

2021년 8월~현재: 성균관대학교 전자전 기컴퓨터공학과 석사과정

[주 관심분야] Frequency Synthesizer 설계

# 신 진 욱 [성균관대학교/석·박사통합과정]

#### https://orcid.org/0009-0005-2535-3237

2022년 2월: 한양대학교 ERICA 전자공학 부 (공학사)

2022년 3월~현재: 성균관대학교 전자전 기컴퓨터공학과 석·박사통합과정

[주 관심분야] Frequency Synthesizer 설계

# 문 준 호 [한화시스템/연구원]

### https://orcid.org/0009-0000-3720-278X

2021년 2월: 경희대학교 전자공학과 (공학 사)

2023년 2월: 성균관대학교 전자전기컴퓨 터공학과 (공학석사)

2023년  $3월\sim$ 현재: 한화시스템 연구원 [주 관심분야] Frequency Synthesizer 설계

# 김 병 성 [성균관대학교/교수]

# https://orcid.org/0000-0003-3084-6499

1989년 2월: 서울대학교 전자공학과 (공학 사)

1991년 2월: 서울대학교 전자공학과 (공학 석사)

1997년 2월: 서울대학교 전자공학과 (공학 박사)

1997년 3월~현재: 성균관대학교 정보통

신대학 교수

[주 관심분야] RFIC 설계, RF 소자 모델링

# 박 세 준 [성균관대학교/석사과정]

#### https://orcid.org/0000-0002-9150-011X

2021년 2월: 성균관대학교 전자전기공학 부 (공학사)

2021년 3월~현재: 성균관대학교 전자전 기컴퓨터공학과 석사과정

[주 관심분야] Frequency Synthesizer 설계