# 140 GHz 40 nm CMOS 저잡음 증폭기

## A 140 GHz Low-Noise Amplifier in 40 nm CMOS

박 채 은 · 서 문 교

Chaeun Park · Munkyo Seo

### 요 약

본 논문에서는 40 nm CMOS 공정을 이용하여 140 GHz 대역의 4단 저잡음 증폭기를 설계하였다. 증폭기의 입력과 출력, 상호 단 간의 매칭은 최하위 2개의 금속층과 최상위 금속 배선층으로 구성된 마이크로스트립 라인으로 이루어졌다. 외부 전원의 내부 인더턴스 영향을 최소화하기 위해 바이패스 커패시터를 이용한 AC 접지를 형성하였다. 이상적인 AC 접지의 경우에 근접한 이득 및 잡음 지수를 고려하여 커패시터의 개수를 선정하였다. D-대역 온웨이퍼 셋업을 이용한 측정 결과, 증폭기의 이득은 15.6 dB, 잡음 지수는 8.8 dB이고 18 mW의 전력을 소모한다. 패드를 포함한 회로의 전체 면적은  $490 \mu\text{m} \times 430 \mu\text{m}$ 이다.

### Abstract

This paper presents a 140 GHz four-stage low-noise amplifier in a 40 nm CMOS process. The input, output, and interstage of the amplifier were matched using a microstrip line (composed of lowest two metal layers and a top metal layer). An AC ground using bypass capacitors was formed to minimize the effect of the internal inductance of the external power supply. The number of capacitors was chosen considering an ideal AC ground case for the ground and noise figures. D-band on-wafer measurements indicated a gain of 15.6 dB, noise figure of 8.8 dB, and power consumption of 18 mW. The circuit area, including the pads, was  $490 \mu\text{m} \times 430 \mu\text{m}$ .

Key words: D-band, Low-Noise Amplifier

### I. 서 론

통신 기술의 발전으로 5G 통신(IMT-2020)이 상용화된 현재 다음 세대(6G) 통신을 위한 연구가 수행되고 있다. 최고 전송 속도 1 Tbps, 지연속도 0.1 ms 성능으로 2030년 경 상용화를 목표로 두고 있다. 140 GHz는 자유공간 전

파 손실이 인접 대역에 비해 낮아 차세대 광대역 통신에 적합하여 6G 통신의 주파수 후보로 꼽힌다<sup>[1]</sup>. D-band 대역의 CMOS 공정 기반 D-band(110~170 GHz) 증폭기 등의 단위 회로와 송수신기에 관해 많은 연구가 보고되었다<sup>[2]~[6]</sup>.

본 논문에서는 6G 통신의 유력 주파수인 140 GHz 대역에서 동작하는 단일 종단(single-ended) 저잡음 증폭기

「본 연구는 IDEC에서 EDA Tool을 지원받아 수행하였음.」

「본 연구는 2021년도 정부(과학기술정보통신부)의 재원으로 정보통신기획평가원의 지원을 받아 수행된 연구임(No. 2021-0-00763, 테라헤르츠 6G 지능형 안테나 소자/구조/네트워크 혁신 융합기술 개발).」

성균관대학교 전자전기컴퓨터공학과(Department of Electrical and Computer Engineering, Sungkyunkwan University)

· Manuscript received March 18, 2022 ; Revised March 29, 2022 ; Accepted March 31, 2022. (ID No. 20220318-028)

· Corresponding Author: Munkyo Seo (e-mail: [mkseo@skku.edu](mailto:mkseo@skku.edu))

를 설계하였다. 단일 종단 구조는 차동 구조에 비해 전력 소모가 적고 면적을 적게 차지하는 장점이 있다. 이 증폭기는 입력과 출력, 상호 단 간의 매칭은 마이크로스트립 라인으로 이루어졌고, 입력 임피던스는 잡음과 이득 특성의 절충 지점으로 그 임피던스를 선택하였다. 외부 전원의 인덕턴스 영향 최소화를 위해 단위 바이패스 커패시터 개수에 따른 이득 및 잡음 지수의 변화를 고려하여 커패시터 개수를 선정하였다. 설계된 증폭기는 40 nm CMOS 공정으로 제작하였다. 제작된 증폭기는 D-대역 온 웨이퍼 측정 셋업을 이용하여 성능 평가를 진행하였다.

## II. 설 계

### 2-1 증폭기 회로 구조

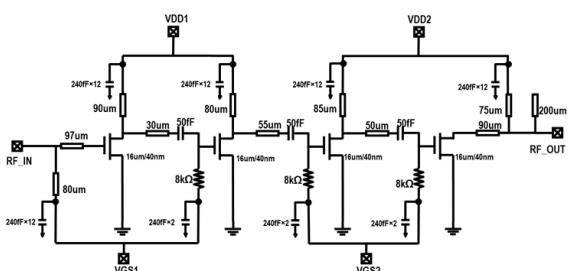

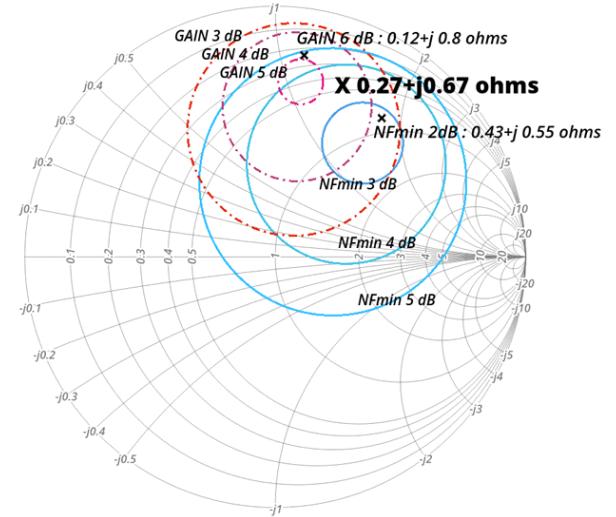

그림 1은 본 논문에서 설계한 140 GHz 저잡음 증폭기 회로도이다. 동작 주파수 대역에서 공통 게이트 대비 이득이 상대적으로 높은 공통 소스 단을 4단 접속하여 약 15 dB 이상의 이득을 갖도록 하였다. 증폭기의 입력 임피던스는 최소 잡음 임피던스와 conjugate 임피던스의 중간 점을 선택하여 잡음과 이득 특성의 절충을 시도하였고, 그림 2는 스미스차트상에서 잡음과 이득이 절충된 임피던스 지점  $50 \times (0.27 + j0.67) \Omega$ 을 보여준다. 단 간 및 출력은 최대 이득을 위한 conjugate 임피던스로 정합하였다. 140 GHz에서 칩상 1/4 파장 전송선의 길이는 약 290  $\mu\text{m}$ 으로 비교적 짧으므로, 집중 소자가 아닌 전송선 기반의 임피던스 정합 회로를 구현하였다. 이는 마이크로스트립 전송선을 사용하였으며, 최하위 2개의 금속층과 최상위

그림 1. 140 GHz 4단 단일 종단 증폭기 회로도

Fig. 1. Schematic of the 140 GHz 4-stage single-ended amplifier.

그림 2. 스미스차트상 입력 임피던스 지점

Fig. 2. Input impedance point at the smith chart.

금속 배선층으로 구성된다. 인접한 단 사이의 커패시터는 단 간 바이어스의 분리 및 임피던스 정합 회로의 역할을 한다.

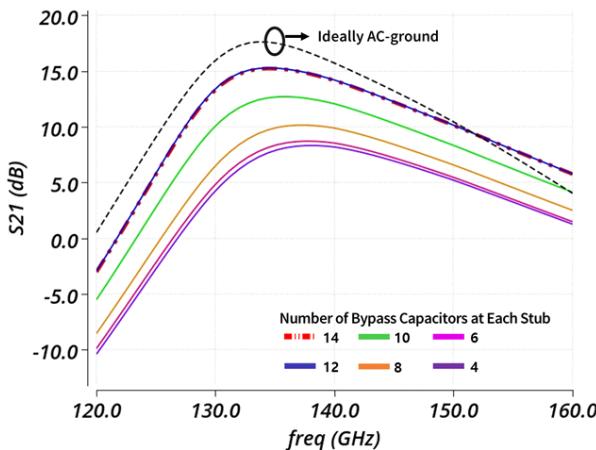

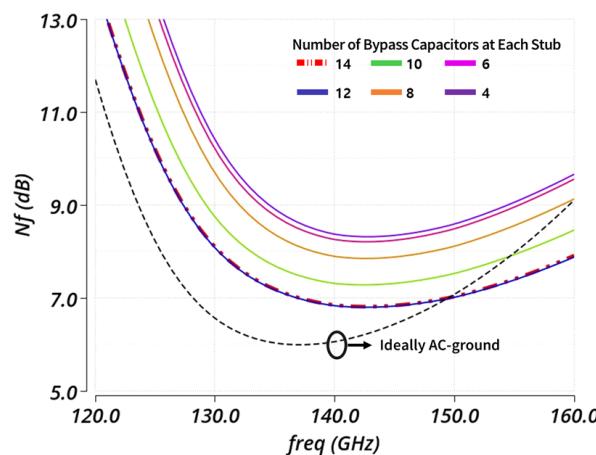

### 2-2 바이패스 커패시터 선정

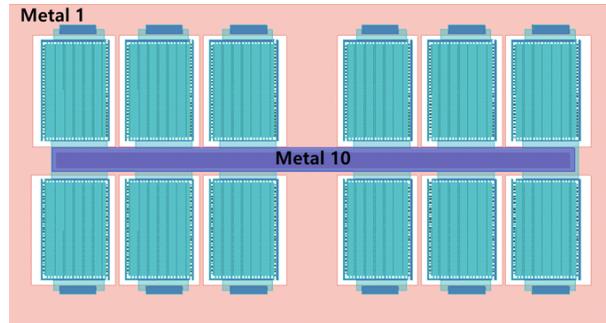

회로와 신호의 대칭성에 의해 가장 접지가 형성되는 차동 구조와 달리 단일 종단 구조의 증폭기는 AC 접지 구현이 필요하다. 본 논문에서는 별도의 바이패스(bypass) 커패시터로 드레인과 게이트 전원 단에 소신호 임피던스가 최소화된 AC 접지를 구현한다. 접지 형성이 완전하지 않다면 외부 전원의 임피던스가 정합에 영향을 미쳐 증폭기 이득 감소, 잡음 지수 증가 등을 초래할 수 있다. 본 설계에서는 트랜지스터에 연결되는 외부 전원이 140 GHz에서 1 KΩ에 가까운 리액턴스를 갖는 내부 인덕턴스 1 nH를 갖는 상황을 가정하여, 이득 손실과 잡음 지수 열화의 최소화를 목적으로 바이패스 커패시터의 조건을 선정하였다. 140 GHz에서 직렬 공진 특성을 갖고, 임피던스가 최소 특성을 나타내는 240 fF 크기의 메탈 핑거 구조의 커패시터를 하나의 단위 바이패스 커패시터로 선정하였다. 그림 3과 그림 4는 1 nH로 가정한 전원 내부 인덕턴스 조건 하에서 단위 바이패스 커패시터 개수에 따른 이득 및 잡음 지수의 변화를 보여준다. 커패시터의 개수

그림 3. 바이패스 커패시터 개수에 따른 이득 변화

Fig. 3.  $S_{21}$  variations with the number of 240 fF unit bypass capacitors.

그림 4. 바이패스 커패시터 개수에 따른 잡음 지수 변화

Fig. 4. Noise figure variations with the number of 240 fF unit bypass capacitors.

를 늘릴수록 이득 및 잡음 지수는 이상적인 AC 접지의 경우에 근접함을 알 수 있다. 12개와 14개인 경우를 비교했을 때, 전자의 경우가 이득이 높고 잡음 지수가 낮았다. 따라서 단위 커패시터의 개수를 12개로 선정하였다. 본 논문의 증폭기 각 전원에는 최종적으로 12개의 단위 바이패스 커패시터(그림 5)를 사용하였으며, 이 때 이득과 잡음 지수는 이상적인 AC 접지와 비교하여 약 1~2 dB 차이로 근접한다. 증폭기의 저면적화 구현을 위해 전송선을 적절히 배치하였으며 모든 전송선 및 내부 연결선은

그림 5. 바이패스 커패시터의 레이아웃 ( $52 \mu\text{m} \times 28 \mu\text{m}$ )

Fig. 5. Layout of bypass capacitors ( $52 \mu\text{m} \times 28 \mu\text{m}$ ).

전자기해석 소프트웨어로 모델링하였다.

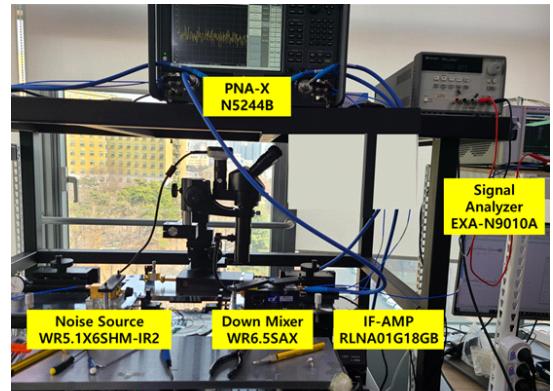

### III. 측정 결과

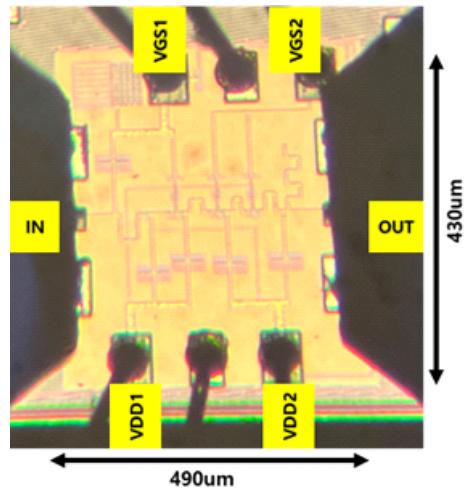

설계된 증폭기는 40 nm CMOS 공정으로 제작하였다. 그림 6은 제작된 140 GHz 증폭기의 칩 사진으로, 패드를 포함한 회로의 크기는  $490 \mu\text{m} \times 430 \mu\text{m}$ 이다. 증폭기 칩을 측정용 PCB에 장착 후 와이어 본딩으로 바이어스를 공급하고, D-대역 온웨이퍼(on-wafer) 측정 셋업을 이용하여 증폭기의 산란 계수 및 잡음 지수를 측정하였다. 아래 모든 측정에서 증폭기의 각 게이트 전압은 모두 0.65 V이고, 드레인 전압은 0.9 V이며 총 소비 전력은 18 mW이다.

그림 6. 140 GHz 저잡음 증폭기 칩 사진

Fig. 6. Chip photo of the 140 GHz low-noise amplifier.

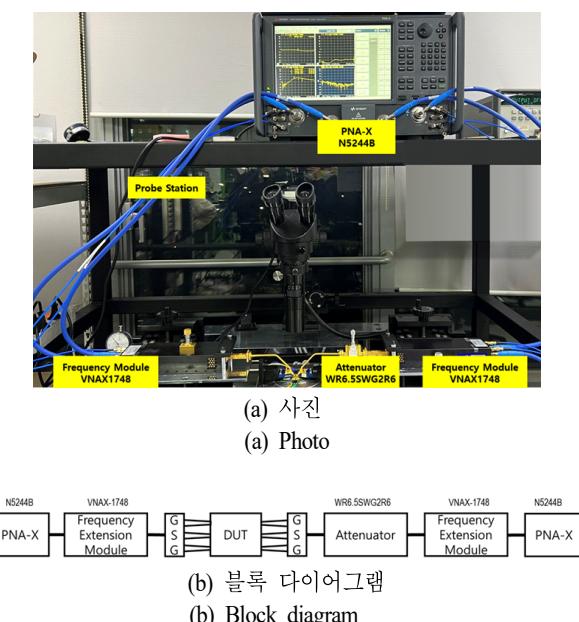

### 3-1 산란 계수 측정

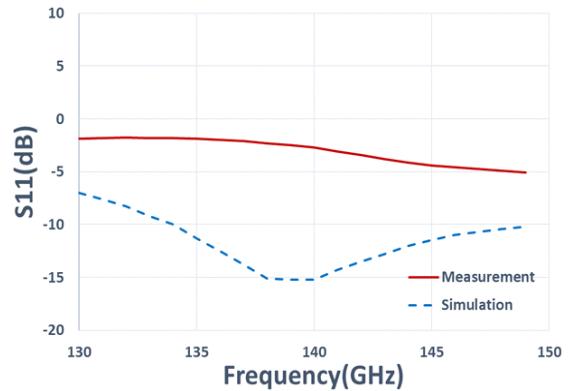

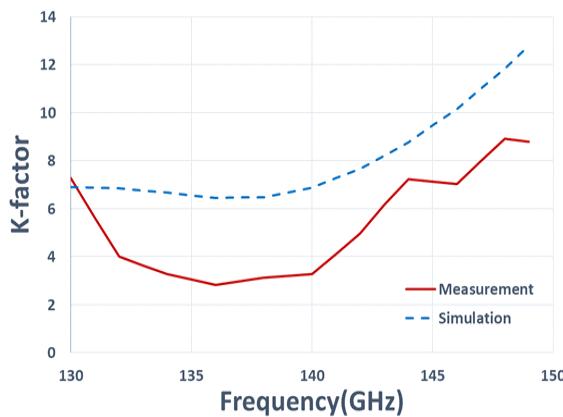

그림 7의 D-대역 온웨이퍼 측정 셋업을 이용하여 증폭기의 산란 계수를 측정하였다. Keysight사의 네트워크 분석기 PNA-X N5244B와 VDI사의 D-대역 주파수 확장 모듈을 사용하였으며, 증폭기의 선형 동작을 위해 입사 전력이  $-20$  dBm 이하가 되게끔 감쇠기를 조절하였다. 측정된 증폭기의 이득(그림 8), 입출력 반사 계수(그림 9, 그

그림 7. D-대역 온웨이퍼 산란 계수 측정 셋업

Fig. 7. D-band on-wafer S-parameter testing setup.

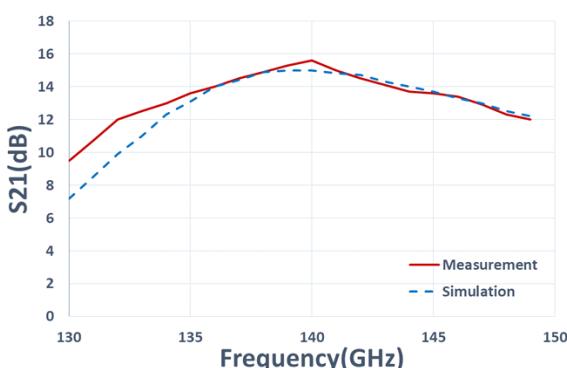

그림 8. 140 GHz 증폭기 이득 측정 결과

Fig. 8. Measured gain of the 140 GHz amplifier.

그림 9. 140 GHz 증폭기 입력 반사 계수 측정 결과

Fig. 9. Measured  $S_{11}$  of the 140 GHz amplifier.

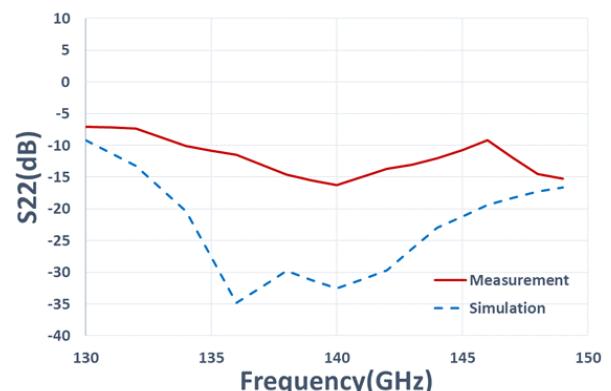

림 10) 및 안정도(그림 11)를 시뮬레이션과 비교하였다. 측정된 증폭기의 최대 이득은 140 GHz에서 15.6 dB이며, 3-dB 대역폭은 약 15 GHz(132 GHz에서 147 GHz)이다. 그림 9와 그림 10에서 보듯이 140 GHz에서 입력 반사 계수는  $-2.7$  dB이고, 출력 반사 계수는  $-16.3$  dB이다. 130 GHz~150 GHz에서 증폭기의 안정도는 1보다 크게 측정되었다. 증폭기의 측정된 이득은 시뮬레이션과  $1\sim2$  dB 차이로 유사하며, 증폭기 입출력 반사 계수의 측정과 시뮬레이션 간의 차이는 능동 소자 및 레이아웃 기생성분의 모델링 오차, 공정 편차, 측정 오차 등에 기인한 것으로 여겨진다. 특히, 입력 반사 계수의 차이는 설계 시 입력 패드의 기생 커패시턴스를 고려하지 않아 생긴 임피던스 부정합으로 여겨진다. 설계 시 패드의 기생성분을

그림 10. 140 GHz 증폭기 출력 반사 계수 측정 결과

Fig. 10. Measured  $S_{22}$  of the 140 GHz amplifier.

그림 11. 140 GHz 증폭기 안정도 측정 결과

Fig. 11. Measured stability factor of the 140 GHz amplifier.

고려한 임피던스 정합이 요구된다.

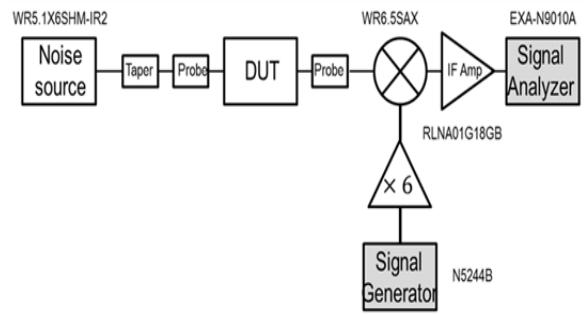

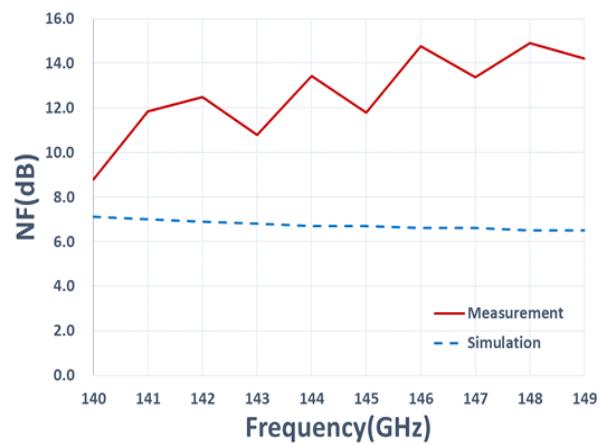

### 3-2 잡음 지수 측정

네트워크 분석기 PNA-X N5244B, VDI사의 140~220 GHz 잡음원 WR5.1NS, D-대역 수신기 모듈 WR6.5SAX, RF-LAMDA사의 IF 증폭기 RLNA01G18GB 및 Keysight사의 신호 분석기 EXA-N9010A를 사용하여 증폭기의 잡음 지수를 측정하였다(그림 12). 그림 13에서 보듯이 140 GHz에서 측정된 잡음 지수는 8.8 dB로 시뮬레이션 결과에 비해 1.6 dB 높은데, 능동 및 수동 소자의 모델링 오차, 공정 편차, 측정 오차 등에 기인한 것으로 여겨진다.

## IV. 결 론

본 논문에서는 40 nm CMOS 기반 140 GHz 4단 단일 중단 공통 소스 증폭기 설계 및 측정 결과를 제시하였다. 설계 시 예측하기 어려운 전원 내부 인더턴스가 존재하더라도 이득 및 잡음 지수의 열화를 최소화할 수 있게 바이пас스 커피시터를 구현하였다. 140 GHz에서 증폭기의 이득 및 잡음 지수는 각각 15.6 dB와 8.8 dB로 측정되었고 18 mW의 전력을 소모한다. 표 1에 기존 논문에 발표된 D-대역 저잡음 증폭기와 비교하였다. 본 논문의 증폭기는 상대적으로 전력 소모가 적고 칩 면적이 작음을 알 수 있다.

(a) 사진

(a) Photo

(b) 블록 다이어그램

(b) Block diagram

그림 12. D-대역 잡음 지수의 측정 셋업

Fig. 12. D-band noise figure testing setup.

그림 13. 잡음 지수에 대한 시뮬레이션과 측정 비교

Fig. 13. Comparison of measured and simulated noise figure.

표 1. D-대역 저잡음 증폭기 성능 비교

Table 1. Comparison of recently published D-band low-noise amplifiers.

| Ref.      | Technology  | Center freq. (GHz) | Topology                 | Peak gain (dB) | 3-dB BW (GHz) | Noise figure (dB) | $P_{dc}$ (mW) | Area including pads (mm <sup>2</sup> ) |

|-----------|-------------|--------------------|--------------------------|----------------|---------------|-------------------|---------------|----------------------------------------|

| [3]       | 22 nm FDSOI | 135                | 4-stage differential LNA | 16             | 40            | 8.5               | 55            | -                                      |

| [4]       | 40 nm CMOS  | 120                | 8-stage single-ended LNA | 20.6           | 40.6          | 6                 | -             | 0.225                                  |

| [5]       | 65 nm CMOS  | 126                | 4-stage single-ended LNA | 14.4           | 17            | 12                | 22.6          | 1.9                                    |

| [6]       | 40 nm CMOS  | 160                | 3-stage differential LNA | 11.6           | 24            | -                 | 42            | 0.29                                   |

| This work | 40 nm CMOS  | 135                | 4-stage single-ended LNA | 15.6           | 15            | 8.8               | 18            | 0.21                                   |

## References

- [1] Y. Xing, T. S. Rappaport, "Propagation measurement system and approach at 140 GHz-moving to 6G and above 100 GHz," in *2018 IEEE Global Communications Conference(GLOBECOM)*, Abu Dhabi, Dec. 2018, pp. 1-6.

- [2] T. H. Jang, D. M. Kang, S. H. Kim, C. J. Lee, H. Park, and J. H. Kim, et al., "120-GHz wideband I/Q receiver based on baseband equalizing technique," *IEEE Journal of Solid-State Circuits*, vol. 56, no. 6, pp. 1697-1710, Jun. 2021.

- [3] A. A. Farid, A. Simsek, A. S. H. Ahmed, and M. J. W. Rodwell, "A broadband direct conversion transmitter/receiver at D-band using CMOS 22 nm FDSOI," in *2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC)*, Boston, MA, Jun. 2019, pp. 135-138.

박 채 은 [성균관대학교/석사과정]

<https://orcid.org/0000-0002-9431-3440>

2020년 8월: 성균관대학교 전자전기공학부 (공학사)

2020년 9월~현재: 성균관대학교 전자전기컴퓨터공학과 석사과정

[주 관심분야] RF, RF Amplifier 등

- [4] T. H. Jang, K. P. Jung, J. S. Kang, C. W. Byeon, and C. S. Park, "120-GHz 8-stage broadband amplifier with quantitative stagger tuning technique," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 67, no. 3, pp. 785-796, Mar. 2020.

- [5] K. Katayama, K. Takano, S. Amakawa, T. Yoshida, and M. Fujishima, "14.4-dB CMOS D-band low-noise amplifier with 22.6-mW power consumption utilizing bias-optimization technique," in *Proceedings of the 2016 IEEE International Symposium on Radio-Frequency Integration Technology(RFIT)*, Taipei, Aug. 2016, pp. 1-3.

- [6] N. Van Thienen, P. Reynaert, "A 160-GHz three-stage fully-differential amplifier in 40-nm CMOS," in *2014 21st IEEE International Conference on Electronics, Circuits and Systems(ICECS)*, Marseille, Dec. 2014, pp. 144-147.

서 문 교 [성균관대학교/부교수]

<https://orcid.org/0000-0002-0691-1783>

1994년 2월: 서울대학교 전자공학과 (공학사)

1996년 2월: 서울대학교 전자공학과 (공학석사)

2007년 12월: University of California, Santa Barbara, USA (공학박사)

2009년~2013년: Teledyne Scientific Company, USA, Senior Engineer

2013년~현재: 성균관대학교 전자전기컴퓨터공학과 부교수

[주 관심분야] Millimeter-Wave & Terahertz IC Design