# 이중 RC 브랜치 회로를 활용한 고고도 전자기파 펄스 발생기의 등가회로 모델링 및 설계

# Modeling and Design of a High-Altitude Electromagnetic Pulse Generator using Double RC Branch Circuits

문 재 식 · 권 종 화\* · 송 익 환

Jaesik Moon · Jong Hwa Kwon\* · Eakhwan Song

요 약

본 논문에서는 고고도 전자기파 펄스 (HEMP, high-altitude electromagnetic pulse) 전도성 방해 내성평가 수행 시 노이즈 소스로 사용되는 이중 지수 펄스 발생기의 등가회로모델을 제안한다. 또한 제안된 등가회로 모델을 이용하여 HEMP 전도성 방해 내성 평가의 다양한 소스 펄스 요구조건을 만족하는 이중 지수 펄스 발생기의 설계법을 제안하였다. 제안된 등가회로 모델을 설계하기 위해서 등가회로모델과 소스 펄스 요구조건 간의 관계를 도출하였다. 제안된 등가회로모델은 HEMP 내성평가 표준에서 제시된 다양한 테스트 모드에 적용되었으며, 인쇄회로기판에 제작된 시료의 측정 결과와 높은 정합성을 보이며 실험적으로 검증되었다.

#### **Abstract**

In this study, an equivalent circuit model of a double exponential pulse generator used as a noise source in a high-altitude electromagnetic pulse (HEMP) conductive disturbance immunity test is proposed. Based on the proposed models, a design methodology for a double exponential pulse generator is presented with various source pulse requirements based on the HEMP conductive disturbance immunity test. To design the proposed equivalent circuit model, the relationship between the equivalent circuit model and source pulse requirements is analyzed and applied to the design methodology with low-impedance conditions. The proposed equivalent circuit model and design methodology are successfully verified experimentally with device-under-test circuits fabricated on printed circuit boards.

Key words: HEMP(High-Altitude Electromagnetic Pulse), Double Exponential Pulse Generator, Equivalent Circuit Model, Double RC Branch Circuit

T. 서 론

20~40 km 이상의 고도에서 핵폭발로 발생하는 고출력 전자기 펄스 (HEMP)에 의해 야기되는 복사성 및 전도

<sup>「</sup>이 논문은 2021년도 광운대학교 우수연구자 지원 사업과 2019년도 정부(과학기술정보통신부)의 재원으로 정보통신기획평가원의 지원(과제번호: 2017-0-00982)을 받아 연구되었음.

광운대학교 전자통신공학과(Department of Electronics and Communications Engineering, Kwangwoon University)

<sup>\*</sup>한국전자통신연구원(Electronic Telecommunication Research Institute)

<sup>·</sup> Manuscript received June 04, 2021; Revised June 21, 2021; Accepted July 15, 2021. (ID No. 20210604-059)

<sup>·</sup> Corresponding Author: Eakhwan Song (e-mail: esong@kw.ac.kr)

성 방해환경은 전자장치 및 시스템의 성능 열화를 유발한다<sup>[1]</sup>. HEMP 방해환경으로부터 전자장치들을 보호하기위해 고출력 전자기 펄스에 대한 영향 평가 및 보호 대책이 수립되었으며, 평가 및 인증시험을 수행할 수 있는 국제 내성평가 기준들이 제정되었다<sup>[2],[3]</sup>. 평가 방법으로는 전자기 펄스의 복사성 영향을 평가하기 위한 SE(shielding effectiveness), CWI(continuous wave immersion) test와 전도성 영향을 평가하기 위한 PCI(pulse current injection) test 등이 있으며, 위 시험들을 통해 방호시설 및 보호 소자의성능을 평가한다<sup>[4],[5]</sup>.

그중 신호선 및 전원선 등 케이블에 결합되어 유기되 는 전도성 전자기 펄스는 주파수 및 시간 영역에서 정의 되며, 내성평가 표준에 적용되기 위한 주파수 범위, 펄스 의 상승 시간, FWHM(full width-half magnitude), 임피던스 및 최대 전압(전류)레벨 등의 다양한 소스 펄스 요구조건 들이 제시된다. BCI(bulk current injection) test 방법으로 수행되는 주파수 영역 전도성 전자기 펄스는 표준에서 요구되는 소스 펄스 요구조건을 frequency modulation 방법 을 통해 비교적 간단하게 만족시킬 수 있다<sup>[6]</sup>. 반면, PCI test 방법을 통해 수행되는 시간 영역 전도성 전자기 펄스 는 표준 내 소스 펄스 요구조건에 따른 test mode가 다양 하기 때문에 이를 모두 만족하는 일반적인 펄스 발생기 모델이 요구된다. 이러한 시간 영역 전도성 전자기 펄스 내성평가에 사용되는 기존 펄스 발생장치는 별도 EM topology tool로 각 test mode를 만족하는 펄스 자체를 생 성하여 사용하거나, 생성된 펄스와 Marx generator와 같은 고전압 승압 장치를 결합하여 펄스를 생성한다<sup>[7]-[9]</sup>. 하지 만 기존 펄스 발생장치는 각 test mode에 따른 시험장치 교체과정이 필요하여 시험의 편의성이 저하되고, 출력 전 압의 가변성이 떨어진다. 또한 여러 장치들이 결합되어 구성되기 때문에 펄스 발생장치 회로의 출력 임피던스 설계가 복잡해지는 어려움이 존재한다.

본 논문에서는 HEMP 전도성 방해 내성평가에 적용되는 기존 펄스 발생장치 설계법의 어려움을 개선하고자이중 RC 브랜치 회로를 활용한 이중 지수 펄스 발생기의 등가회로모델을 제안하였다. 제안된 등가회로모델은 이중 RC 브랜치 구조의 펄스 발생 회로로써, 양의 펄스 전류와 음의 펄스 전류를 생성하고, 이를 조합하여 이중 지

수 펄스를 생성한다. 또한 제안된 표준에서 제시되는 다양한 소스 펄스 요구조건 및 test mode를 만족하도록 소스 펄스 요구조건과 제안된 등가회로모델 간 관계식을 도출하였다. 도출된 관계를 기반으로 low impedance condition을 등가 회로모델에 적용하여 이중 지수 펄스 발생기의 등가회로 설계법을 제시하였다. 제안된 등가회로모델과설계법은 인쇄회로기판에 설계 제작된 시료의 측정을 통해 높은 정합성과 함께 실험적으로 검증되었다.

### Ⅱ. 제안된 이중 지수 펄스 발생기 등가회로모델

본 장에서는 이중 RC 브랜치 구조의 이중 지수 펄스 발생기 등가회로모델이 제안되었다. 제안된 등가회로모 델을 적용하여 일반적인 HEMP 내성평가 표준이 공통적 으로 요구하는 소스 임피던스 요건 및 펄스 파형 요구조 건(펄스 상승시간, FWHM, 첨두 전류)을 모두 만족하는 이중 지수 펄스의 설계가 가능하며, 이를 위해 소스 펄스 요구조건과 제안된 등가회로모델 간 관계가 도출되었다.

#### 2-1 전도성 노이즈 소스로서의 이중 지수 펄스

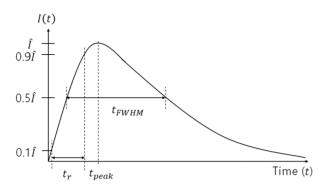

그림 1은 이중 지수 함수로 정의되는 시간 영역 전도성 방해 노이즈 소스이며, 식 (1)의 전류식으로 정의된다<sup>[5]</sup>.

$$I(t) = K_{DE} \hat{I}(e^{-\alpha t} - e^{-\beta t})$$

(1)

그림 1 및 식 (1)에서의 파라미터 정의는 다음과 같다.

$K_{DE}$ : 펄스 전류의 크기 보정계수  $\hat{I}$ : 펄스 전류가 최댓값을 가지는 첨두 전류값 lpha,eta: 이중 지수 펄스의 특성 파라미터  $t_r$ : 펄스의 크기가 10 %에서 90 %까지 도달하는데 소요되는 시간

$t_{fwhm}$ : 펄스 전류가  $0.5\,\hat{I}$  인 지점의 시간 간격  $t_{peak}$ : 첨두 전류값  $\hat{I}$  에서의 시간

생성된 이중 지수 펄스는 양의 부호를 유지하기 위해 식 (2)를 항상 만족해야 한다.

$$0 < \alpha < \beta \,, \ t \ge 0 \tag{2}$$

그림 1. 시간영역 전도성 노이즈 소스

Fig. 1. Time domain conducted noise source.

#### 2-2 제안된 등가회로모델

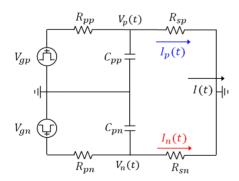

그림 2는 이중 지수 펄스를 생성하기 위해 제안된 등가 회로모델이며, 이중 RC 브랜치 구조로 구성된다. 각각의 RC 브랜치 회로는 같은 크기와 서로 다른 시상수 및 부호를 가지는 스텝 펄스 전류  $I_p(t)$ ,  $I_n(t)$ 를 생성하고, 그 조합으로 이중 지수 펄스를 생성하며, 저항과 캐패시터, 스텝 펄스의 설계를 통해 다양한 소스 펄스 요구조건을 만족하는 이중 지수 펄스를 생성한다. 등가회로모델 내 회로소자 및 용어 정의는 다음과 같다.

R: 소스 임피던스 저항

$R_n$ ,  $C_n$ : 펄스 성형회로 저항, 캐패시터

$V_a$ : 스텝 펄스 발생기

펄스 성형회로:  $R_p$ ,  $C_p$  및  $V_g$  를 포함하여 펄스의 시상  $\phi$  및 부호를 조절하는 회로

그림 2. 제안된 등가회로모델

Fig. 2. Proposed equivalent circuit model.

양의 펄스 생성회로:  $R_{sp}$ ,  $R_{pp}$ ,  $C_{pp}$  및  $V_{sp}$ 를 포함하 브랜 치 회로

음의 펄스 생성회로:  $R_{sn}$ ,  $R_{pn}$ ,  $C_{pn}$  및  $V_{gn}$ 을 포함하는 브래치 회로

#### 2-3 이중 지수 펄스 모델링

본 절에서는 다양한 test mode를 만족하는 일반적인 이중 지수 펄스 발생기 등가회로모델을 설계하기 위해 제안된 등가회로의 수식 모델을 제안한다. 표 1은 IEC (international electrotechnical commission) 61000-4-24 HEMP 내성평가 표준 내 test mode이며, 해당 표준 외 일반적인 HEMP 내성평가 표준들은 모두 이와 같은 소스 펄스 요구조건과 test mode를 제시한다.

표 2는 소스 펄스 요구조건과 제안된 등가회로모델 간

#### 표 1. IEC 61000-4-24 conducted early-time HEMP (CEP) 소스 펄스 요구조건

Table 1. Conducted early-time HEMP (CEP) source pulse requirements in IEC 61000-4-24.

| Туре                        | $CEP_1$  | $CEP_4$  | $CEP_6$  |

|-----------------------------|----------|----------|----------|

| Rise time (ns)              | <10      | <10      | <10      |

| FWHM (ns)                   | 100±30 % | 500±30 % | 500±10 % |

| Peak current (kA)           | 4±10 %   | 04.±10 % | 5±10 %   |

| Source impedance $(\Omega)$ | 400±15   | 50±5     | ≥60      |

표 2. 소스 펄스 요구조건과 등가회로모델 간 관계식

Table 2. Relationship between source pulse requirements and equivalent circuit model.

| Source pulse requirements | Equivalent circuit model                                                                                                                                 |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| α                         | $\frac{1}{\left(R_{pp} \  R_{sp}\right) C_{pp}}$                                                                                                         |

| β                         | $\frac{1}{\left(R_{pn}\ R_{sn}\right)C_{pn}}$                                                                                                            |

| $t_{peak}$                | $\frac{1}{\beta - \alpha} \left( \ln \left( \frac{\alpha}{\beta} \right) \right)$                                                                        |

| $\hat{I}$                 | $rac{V_g}{R_p + R_s} (e^{-lpha t_{peak}} - e^{-eta t_{peak}})$                                                                                          |

| $K_{DE}$                  | $\left\{ \left(\frac{\alpha}{\beta}\right)^{\frac{\beta}{\beta-\alpha}} - \left(\frac{\alpha}{\beta}\right)^{\frac{\alpha}{\beta-\alpha}} \right\}^{-1}$ |

도출된 관계를 보여주며, 관계 도출을 위해 표준에서 정의된 전류식과 제안된 등가회로모델의 출력 전류식을 비교한다. 회로모델의 출력 전류는 2개의 RC 브랜치 회로에서 생성되는 펄스 전류들을 조합하여 이중 지수 펄스파형으로 생성된다. 이 때 양의 펄스 생성회로에서 생성되는 전류  $I_p(t)$ 는 식 (3)과 같이 정의되며, 음의 펄스 생성 회로에서의 전류  $I_n(t)$  또한 동일한 형태를 가진다. 전체전류 I(t)는 두 전류의 합으로 식 (4)와 같이 정의된다.

$$I_p(t) = \frac{V_p(t)}{R_{sp}} = \frac{V_p(t)}{R_{sp}} \left( 1 - e^{\frac{t}{\tau_p}} \right)$$

(3)

$$\begin{split} I(t) &= I_p(t) + I_n(t) = \frac{V_{gp}}{R_{pp} + R_{sp}} \bigg( 1 - e^{-\frac{t}{\tau_p}} \bigg) \\ &+ \frac{V_{gn}}{R_{pp} + R_{sn}} \bigg( 1 - e^{-\frac{t}{\tau_n}} \bigg) \end{split}$$

where

$$\tau_p = (R_{pp} \| R_{sp}) C_{pp}$$

,  $\tau_n = (R_{pm} \| R_{sn}) C_{pn}$  (4)

제안된 등가회로모델의 출력 전류 식 (4)와 HEMP 내성평가 표준에서 정의된 식 (1)은 등가관계가 성립하므로식 (1)의 파라미터와 제안된 등가회로모델 소자 간 관계를 도출할 수 있으며, 식 (5)의 이중 지수 펄스의 경계 조건을 식 (4)에 적용하여 식 (6)의 조건을 얻을 수 있다. 추가로 전류식 I(t)를 미분하여  $t_{peak}$ 와  $\hat{I}$ 을 정의할 수 있고, 식 (6)을 활용한 식 (1)과 (4)의 계수 비교를 통해 표 2의 소스 펄스 요구조건과 등가회로모델 간의 관계를 도출한다.

$$\lim_{t \to \infty} I(t) = 0 \tag{5}$$

$$\frac{V_{gp}}{R_{pp} + R_{sp}} + \frac{V_{gn}}{R_{pn} + R_{sn}} = 0 {6}$$

#### Ⅲ. 등가회로모델 기반 이중 지수 펄스 발생기 설계

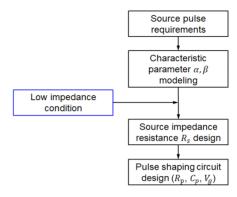

본 장에서는 2장에서 도출된 등가회로모델과 소스 펄스 요구조건간 관계를 기반으로 제안된 등가회로모델을 설계한다. 그림 3은 제안된 등가회로모델의 설계 흐름도이며, 이중 지수 펄스의 소스 펄스 요구조건을 모두 만족하는 등가회로를 설계하기 위해 소스 임피던스 저항  $R_s$ , 펄스 성형회로 소자  $R_p$ ,  $C_p$  및 스텝 펄스 발생기  $V_g$ 를 설

그림 3. 등가회로모델 설계 흐름도

Fig. 3. Design flow of equivalent circuit model.

계한다.

#### 3-1 특성 파라미터 모델링

이중 지수 펄스의 전류식은 특성 파라미터  $\alpha,\beta$  를 포함하는 2개의 지수항으로 구성되는데, 특성 파라미터를 지수함수의 계수로 가지며 비선형 함수이기 때문에, 분석적인 일반해가 존재하지 않는다. 본 논문에서 제안하는설계법은 HEMP 내성평가 표준에서 주어지는 소스 펄스요구조건을 만족하는 이중 지수 펄스를 설계하는데 그목적이 있기 때문에, 펄스의 파형 특성을 결정하는 특성파라미터와 소스 펄스요구조건 간 관계를 정의해야 한다. 파라미터 X,Y는 기존의 특성 파라미터 근사 방법의낮은 정확도를 개선하기 위해 Nelder-Mead 알고리즘의반복적 접근으로 추출된 근사 파라미터이며, 소스 펄스요구조건과 결합하여 근사식 (7), 4(8)과 같이 특성 파라미터를 모델링할 수 있다[10],[11]

$$\alpha = \frac{1}{t_r} \left[ \frac{X_1}{((t_{fwhm}/t_r)^{X_2} - X_3)^{X_4}} \right]$$

(7)

$$\beta = \frac{1}{t_r} \left[ Y_1 - Y_2 e^{\frac{t_{fwhm}}{t_r} Y_3} - Y_4 e^{\frac{t_{fwhm}}{t_r} Y_5} - Y_6 e^{\frac{t_{fwhm}}{t_r} Y_7} \right]$$

(8)

#### 3-2 소스 임피던스 저항 설계

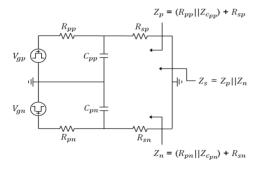

본 절에서는 모델링된 특성 파라미터를 활용하여 제안 된 등가회로모델이 소스 임피던스 요건을 만족하도록 설 계한다. 표 1의 소스 임피던스  $Z_s$  는 기준 임피던스와 임 피던스 에러  $Z_s$  의 합차형태로 정의되며, 제안된 등가회로모델의 전체 출력 임피던스가 만족해야 한다. 그림 4는 제안된 등가회로모델의 출력 임피던스를 보여준다.

하나의 RC 브랜치 회로의 임피던스는 펄스 성형회로 의 임피던스와 소스 임피던스 저항  $R_s$  의 합으로 구성되 며, 제안된 등가회로모델의 출력 임피던스는 2개의 RC 브랜치 회로의 출력 임피던스를 병렬 합성하여 정의된다. 본 논문에서는 소스 임피던스 요건을 만족하는 등가회로 모델을 설계하기 위해 펄스 성형회로의 임피던스를 제한 하는 조건으로 low impedance condition을 제안하였다. 하 나의 RC 브랜치 회로의 출력 임피던스가 표준의 소스 임 피던스의 2배를 만족해야 하기 때문에, low impedance condition은 식 (9)와 같이 정의되어 펄스 성형회로의 임피 던스를 제한한다. Low impedance condition이 적용됨에 따 라 임피던스의 오차값으로 근사된 펄스 성형회로의 임피 던스는 매우 작기 때문에 식 (10), (11)과 같이 소스 임피 던스 저항  $R_s$  를 하나의 RC 브랜치 회로의 출력 임피던스 로 근사할 수 있다. 전체 출력 임피던스는 식 (12)와 같이 각 RC 브랜치회로의 임피던스 병렬 합성으로 나타나므 로, 소스 임피던스 저항  $R_s$  만으로 표준의 소스 임피던스 요건 Z<sub>3</sub> 를 충족시킬 수 있다.

$$|R_p|||Z_{C_e}| \le 2Z_e \tag{9}$$

$$Z_p = |R_{pp}| |||Z_{C_{pp}}| + R_{sp} \le R_{sp} + 2Z_e \cong R_{sp}$$

(10)

$$Z_n = |R_{pn}| |||Z_{C_{pn}}| + R_{sn} \le R_{sn} + 2 Z_e \cong R_{sn}$$

(11)

그림 4. 등가회로모델 출력 임피던스

Fig. 4. Output impedance of equivalent circuit model.

$$Z_s = Z_p \| Z_n \cong R_{sp} \| R_{sn} \tag{12}$$

Low impedance condition을 등가회로모델에 적용하여 소스 임피던스 저항  $R_s$ 를 결정한 후, 펄스 성형회로를 설계하기 위해 식 (9)를  $R_p$  에 대하여 전개한다. 표 2에서 도출된 특성 파라미터와 등가회로모델 간 관계를 활용하여  $\alpha$ 의 관계식을  $C_{pp}$  에 대하여 정리할 수 있고, 이를 식 (9)에 대입하여 양의 펄스 성형회로 저항  $R_{pp}$  에 대하여 정리하면 식 (13)과 같다. 또한 제안된 등가회로 모델은 동일한 구조의 RC 브랜치 회로로 구성되므로 음의 펄스 성형회로도 동일한 과정으로 식 (14)와 같이 정리할 수 있다.

$$\begin{split} &(1-B_p)R_{pp}^2 - 2\,R_{sp}B_pR_{pp} - (4\,Z_e^2 + B_pR_{pp}^2) < 0 \quad \text{(13)} \\ &\text{where } B_p = \frac{4\,Z_e^2\,\omega^2}{\alpha^2\,R_{sp}^2}\,, \; \alpha = \frac{1}{(R_{pp}\|R_{sp})\,C_{pp}} \end{split}$$

$$\begin{split} &(1-B_n)R_{pn}^2 - 2\,R_{sn}B_nR_{pn} - (4\,Z_e^2 + B_nR_{pn}^2) < 0 \quad \text{(14)} \\ &\text{where } B_n = \frac{4\,Z_e^2\,\omega^2}{\beta^2\,R_{sn}^2}\,, \; \beta = \frac{1}{(R_{pn}\|R_{sn})\,C_{pn}} \end{split}$$

식 (13), 식 (14)를  $R_{pp}$ ,  $R_{pn}$ 에 관하여 정리하기 위해  $R_p$ 의 2차항 계수의 부호를 확인해야 하며, 계수로 존재하는 파라미터 B는 항상 양수이기 때문에 최댓값을 기준으로 1과 비교해야 한다. 파라미터 B는 특성 파라미터, 소스 임피던스 저항, 임피던스 에러 및 주파수로 구성된다. 이 때분모의 특성 파라미터가 다른 구성요소들에 비해 매우큰 값을 가지기 때문에 1보다 항상 작아 2차 부등식을 전개하여 식 (15)및 식 (16)과 같이 소스 임피던스 요건을 만족하는  $R_p$ 의 최대값 범위를 얻을 수 있으며, 주파수 범위를 결정함으로써 최대값 또한 얻을 수 있다.

$$\begin{split} R_{pp} < k_p & \text{ where } \\ k_p = 0.5 \left[ \frac{2 R_{sp} B_p}{1 - B_p} + \sqrt{\left( \frac{2 R_{sp} B_p}{1 - B_p} \right)^2 + 4 \left( \frac{4 Z_e^2 + B_p R_{sp}^2}{1 - B_p} \right)} \right] \end{split}$$

$$R_{pn} < k_n$$

(16) where

$$k_n = 0.5 \left[ \frac{2R_{sn}B_n}{1 - B_n} + \sqrt{\left(\frac{2R_{sn}B_n}{1 - B_n}\right)^2 + 4\left(\frac{4Z_e^2 + B_nR_{sn}^2}{1 - B_n}\right)} \right]$$

#### 3-3 펄스 성형회로 설계

본 절에서는 앞서 도출된 소스 임피던스 저항  $R_s$ 의 최대 범위로부터 값을 결정한 후, 필스 성형회로 소자  $R_p$ ,  $C_p$  및 스텝 필스 발생기의 크기  $V_g$  를 설계한다. 식 (17)과식 (18)은 표 2에서 정의된 특성 파라미터와 등가회로모델 간 관계식을 활용하여 필스 성형회로의 캐패시터  $C_p$ 에 대하여 정리한 식이다. 앞서 결정된 특성 파라미터 모델링과 소스 임피던스 저항  $R_s$ 와 도출된 최대값 범위에서  $R_p$ 를 결정함으로써 필스 성형회로의 캐패시터  $C_p$ 를 결정할 수 있다.

$$C_{pp} = \frac{1}{(R_{pp} || R_{sp})\alpha} \tag{17}$$

$$C_{pn} = \frac{1}{(R_{pn} || R_{sn})\beta} \tag{18}$$

소스 임피던스 저항  $R_s$  및 펄스 성형회로 소자  $R_p$ ,  $C_p$ 를 모두 결정한 후, 스텝 펄스 발생기  $V_{gp}$ ,  $V_{gp}$ 을 설계한다. 스텝 펄스 발생기의 크기는 첨두 전류값을 통해 결정되며, 첨두 전류값은 표 2에서 정의된 관계식을 통해 결정한다. RC 브랜치 회로 각각의 스텝 펄스 발생기 크기  $V_{gp}$ ,  $V_{gp}$ 은 이중 지수 펄스의 경계 조건을 활용하여 얻은 식 (6)을 활용하여 식 (19), 식 (20)과 같이 결정할 수 있다.

$$V_{m} = A(R_{m} + R_{sn}) \tag{19}$$

$$V_{gn} = -A(R_{pn} + R_{sn})$$

where  $A = K_{DE} \hat{I}$  (20)

#### Ⅳ. 설계 예시 및 검증

본 장에서는 HEMP 내성평가 표준에서 제시된 다양한 test mode 중 몇 가지를 채택하여 제안된 등가회로모델과 설계 방법을 적용한다. 제안된 설계법으로 도출된 설계수치를 적용하여 회로 시뮬레이션 결과와 표준 내 소스 펄스 요구조건을 비교하였다. 또한 제안된 등가회로를 적용하여 인쇄회로기판에 설계 제작된 시료의 측정 결과와의 비교를 통해 제안된 등가회로모델과 설계 방법을 실험적으로 검증하였다.

#### 4-1 설계 예시

제안된 등가회로모델에 적용된 설계 방법의 적용 순서 는 아래와 같다.

- 1) 특성 파라미터 모델링

- 2) Low impedance condition 적용을 통한 소스 임피던스 저항 Rs 설계

- 3) 펄스 성형회로 및 스텝 펄스 발생기 설계

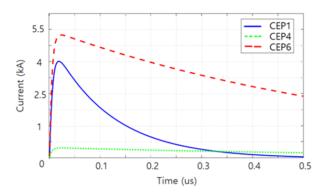

본 절에서는 표 1의 CEP1 test mode를 채택하여 설계하 였으며, 이중 지수 펄스가 만족해야 하는 소스 펄스 요구 조건이 명시되어 있다. 소스 펄스 요구조건 내 펄스 파형 요건 (펄스 상승시간  $t_r=9$  ns 및 FWHM  $t_{flwm}=100$  ns)을 식 (7), 식 (8)에 대입하여 특성파라미터 ( $\alpha$ =17.3 $\times$ 10 $^{7}$ ,  $\beta$ =  $8.6 \times 10^{6}$ )를 결정한다. 설계에 적용된 주파수 범위는 통상 적인 HEMP 환경에서의 주파수 범위인 100 kHz~ 200 MHz로 적용되었다. 소스 임피던스 저항  $R_s$  는 펄스 성형 회로에 low impedance condition을 적용한 식 (12)에 의해  $R_{sp}$ ,  $R_{sp}$ =800  $\Omega$ 으로 결정된다. 펄스 성형 회로 저항  $R_{p}$ 는 결정된 소스 임피던스 저항과 특성 파라미터 및 식 (15), (16)에 의해  $R_{pp}$ ,  $R_{pn}$  < 30  $\Omega$ 의 최대 범위를 얻을 수 있다. 도출된 범위 내에서  $R_{pp}$ ,  $R_{pm}$ 을 20  $\Omega$ 으로 결정하였고, 펄 스 성형회로의 캐패시터  $C_{pp}$ ,  $C_{m}$ 은 식(17), 식(18)로, 스텝 펄스 발생기의 크기  $V_{gp}$ ,  $V_{gn}$ 는 식 (19), 식 (20)를 활용해 설계할 수 있다. 표 3은 제안된 등가회로모델 및 설계법 을 적용하여 도출한 CEP1, CEP4, CEP6 mode 설계 파라 미터이다. 그림 5는 세가지 mode의 설계 수치를 HFSS 회로 시뮬레이션에 적용해 얻은 이중 지수 펄스 전류 파 형이다. 표 4는 세가지 모드의 회로 시뮬레이션과 소스

표 3. 테스트 mode 별 설계 파라미터 Table 3. Design parameters by test mode.

|         | $R_s(\Omega)$ | $R_p(\Omega)$ | $C_p$ (nF) | $C_n$ (nF) | $V_{gp}$ (MV) | V <sub>gn</sub> (MV) |

|---------|---------------|---------------|------------|------------|---------------|----------------------|

| $CEP_1$ | 800           | 20            | 0.29       | 30.59      | 4.04          | -4.04                |

| $CEP_4$ | 100           | 10            | 0.496      | 75.11      | 0.05          | -0.05                |

| $CEP_6$ | 140           | 15            | 0.334      | 50.38      | 0.81          | -0.81                |

그림 5. CEP1 mode 펄스 전류 시뮬레이션 파형 Fig. 5. CEP1 mode pulse current simulation waveform.

표 4. 테스트 모드별 회로 시뮬레이션과 소스 펄스 요구 조건간의 파라미터 비교

Table 4. Parameter comparison of circuit simulation and source pulse requirements by test mode.

| Туре                        | Rise time (ns) | FWHM (ns) | Peak current (kA) | Source impedance $(\Omega)$ |

|-----------------------------|----------------|-----------|-------------------|-----------------------------|

| $CEP_1$                     | 10<            | 100±30 %  | 4±10 %            | 400±15                      |

| CEP <sub>1</sub> simulation | 9.04           | 101.12    | 4.0026            | 401.4~410                   |

| $CEP_4$                     | 10<            | 500±30 %  | 0.4±10 %          | 50±5                        |

| CEP <sub>4</sub> simulation | 9.2            | 496.52    | 0.41              | 50.8~54.8                   |

| $CEP_6$                     | 10<            | 500±10 %  | 5±10 %            | ≥60                         |

| CEP <sub>6</sub> simulation | 9.34           | 101.12    | 5.02              | 71.1~77.1                   |

펄스 요구조건간의 파라미터 비교로, 제안된 등가 회로모 델과 설계법을 적용하여 내성평가표준 내 소스 펄스 요 구조건을 만족하는 이중 지수 펄스를 설계할 수 있다.

#### 4-2 측정 검증

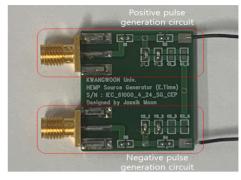

제안된 등가회로모델과 설계 방법을 적용한 이중 지수 펄스 생성을 위해 펄스 생성회로 및 측정 셋업을 구성하 였다. 그림 6은 인쇄회로기판에 제작된 이중 지수 펄스 생성 회로이며, 스텝 펄스 입력을 받기 위한 커넥터와 제 안된 등가회로모델 회로로 구성되어 있다. 그림 7은 측정

그림 6. 이중 지수 펄스 생성 회로

Fig. 6. Double exponential pulse generation circuit.

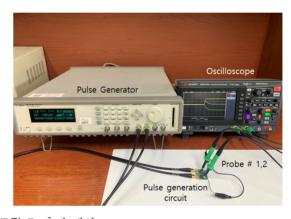

그림 7. 측정 셋업

Fig. 7. Measurement setup.

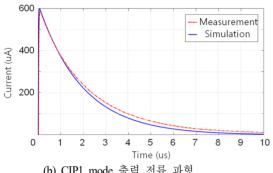

셋업으로 Kesight 81110A 펄스 발생기에서 양, 음의 전압스텝 펄스를 입력받아 제안된 설계법으로 얻은 설계치를 적용한 펄스 생성 회로를 통해 이중 지수 펄스를 생성한다. 측정은 Keysight DSOX1204 digital oscilloscope와 200 MHz 대역 프로브를 사용하였다. HEMP 내성평가 기준IEC 61000-4-24 내 early-time pulse(CEP)와 intermediate-time pulse (CIP) 총 2개의 test mode 이중 지수 펄스를 생성하였으며, 제안된 등가회로모델과 설계 방법으로 설계된 회로 시뮬레이션 기반 이중 지수 펄스 발생기 모델과시료 제작을 통해 생성된 펄스를 측정하여 소스 펄스 요구조건을 기준으로 정합성을 관찰하였다.

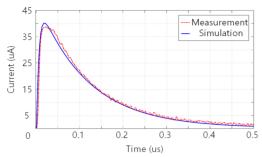

그림 8은 CEP1 test mode 및 CIP1 test mode 기반 출력 전류 파형을 보여준다. 측정을 진행할 때 표준에서 제시되는 첨두 전류값의 경우, 실험실 단계에서 위험도가 크고,

- (a) CEP1 mode 출력 전류 파형

- (a) CEP1 mode output current waveform

- (b) CIP1 mode 출력 전류 파형

- (b) CIP1 mode output current waveform

그림 8. IEC 61000-4-24 기반 출력 전류 파형

Fig. 8. Output current waveform based on IEC 61000-4-24.

제안된 등가회로모델 및 설계법으로 생성된 이중 지수 펄스의 정합성 관찰에 그 목적이 있기 때문에, 측정 검증 에 사용되는 스텝 펄스 발생기의 안정적 출력범위를 고 려하여 전압 및 전류의 크기를 10<sup>8</sup>만큼 scale-down 하여 mV, uA 단위에서 측정하였다. 표 5와 표 6은 제안된 모델

표 5. Scale-down이 적용된 CEP1 mode에서의 제안된 모 델과 측정간의 파라미터 비교

Table 5. Parameter comparison of proposed equivalent model and measurement in CEP1 mode with applied scale down.

| CEP1                      | Rise time (ns) | FWHM (ns) | Peak current ( $\mu$ A) |

|---------------------------|----------------|-----------|-------------------------|

| Source pulse requirements | <10            | 100±30 %  | 40±10 %                 |

| Proposed                  | 9              | 100       | 40                      |

| Measured                  | 7.5            | 95.5      | 37.2                    |

| Error (%)                 | 16.7           | 7         | 4.5                     |

표 6. Scale-down이 적용된 CIP1 mode에서의 제안된 모 델과 측정간의 파라미터 비교

Table 6. Paraameter comparison of proposed equivalent model and measurement in CIP1 mode with applied scale down.

| CIP1                      | Rise time (µs) | FWHM (ms) | Peak current ( μ A) |

|---------------------------|----------------|-----------|---------------------|

| Source pulse requirements | <25            | 1.5±30 %  | 600±10 %            |

| Proposed                  | 25.3           | 1.5       | 599                 |

| Measured                  | 26             | 1.47      | 593                 |

| Error (%)                 | -2.6           | 2         | 1                   |

과 측정 간의 CEP1. CIP1 test mode 별 소스 펄스 요구조건 비교표이며, 표준 내 요구조건에 만족됨을 확인할 수 있 고, 제안된 모델과 측정간의 정합성 또한 확인할 수 있다. 본 논문에서는 이중 지수 펄스 발생기의 등가회로모델 및 설계방법을 제안하고 검증하였으며, 연구실 단위에서 의 이중 지수 펄스의 정합성 관찰을 목적으로 측정 환경 의 구성, 소자 선정 및 이중 지수 펄스 생성 회로의 구현 이 이루어졌다. 하지만 실제 고전압 펄스 생성을 위해선 적용되는 소자의 내압, 기생 성분, 이격거리 및 차폐실 유 무등이 고려되어야 하며, 제안하는 등가회로모델은 2개 의 스텝 펄스 입력을 사용하기 때문에 입력 스텝 펄스의 폭, 발생 시간의 동기화 등을 고려해야 한다. 특히 생성하 고자 하는 이중 지수 펄스가 빠른 시간 대역으로 갈수록 커패시터의 충방전 특성에 따른 입력 스텝 펄스의 상승 시간과 두 입력 펄스의 발생시간 동기화에 어려움이 존 재하여, 이에 대한 추가적인 분석이 필요할 것으로 사료 된다. 또한 실제 소자에서 발생할 수 있는 오차의 영향이 본 연구에서는 반영되지 않은 한계점이 존재하며, 본 연 구결과의 실용성을 추가 확보하기 위해서는 소자 오차 분포가 고려된 통계적 분석 기반 모델링과 설계방법론에 대한 후속 연구가 이루어져야 할 것으로 사료된다.

#### V. 결 론

본 논문에서는 기존 전도성 방해 내성평가에 적용되는 기존 펄스 발생장치 설계법을 개선하고자 이중 RC 브랜 치 회로를 활용한 이중 지수 펄스 발생기의 등가회로모 델을 제안하고 설계하였다. 이중 지수 펄스 발생기 등가 회로의 수식 모델이 제안되었으며, 표준에서 제시되는 다양한 소스 펄스 요구조건을 만족하기 위해 소스 펄스 요구조건과 등가회로모델 간 관계식을 도출하고, 이중 지수 펄스 발생기의 등가회로 설계법을 제시하였다. 제안된 등가회로모델과 설계법을 활용하여 설계 시 등가회로만으로 출력 임피던스 및 펄스 성형이 모두 가능하여 기존 펄스 발생장치의 시험 편의성 및 출력 임피던스 조절의 어려움을 개선, 고출력 HEMP 전도성 방해 내성평가가가지는 시간 및 비용적 한계점을 극복할 수 있을 것으로 사료된다.

#### References

- [1] R. Hoad, W. A. Radasky, "Progress in high-altitude electromagnetic pulse (HEMP) standardization," *IEEE Transactions on Electromagnetic Compatibility*, vol. 55, no. 3, pp. 532-538, Jun. 2013.

- [2] Electromagnetic Compatibility (EMC), Part 2-10: Environment Description of HEMP Environment Conducted Disturbance, IEC 61000-2-10, 1998.

- [3] Electromagnetic Compatibility (EMC), Part 5: Installation and Mitigation Guidelines - Section 5: Specification of Protective Devices for HEMP Conducted Disturbance, Basic EMC Publication, IEC 61000-5-5, 1996.

- [4] Department of Defense Interface Standard: High-Altitude Electromagnetic Pulse(HEMP) Protection for Ground-Based C4I Facilities Performing Critical, Time Urgent Missions, Part 1 - Fixed Facilities, MIL-STD-188-1, 1998.

- [5] Electromagnetic Compatibility(EMC), Part 4: Testing and Measurement Techniques - Test Methods for Protective

- Devices for HEMP Conducted Disturbance, IEC 61000-4-24, 2015.

- [6] Electromagnetic Compatibility(EMC), Part 4: Testing and Measurement Techniques - Immunity to Conducted Disturbance, Inducted by Radio-Frequency Fields, EC 61000-4-6, 2013.

- [7] Y. J. Kim, H. J. Kang, Y. K. Jeong, D. K. Youn, and Y. B. Park, "Analysis and performance improvement of integrated el pulse generator for emP protection performance test," *Journal of Korean Institute of Electromagnetic Engineering and Science*, vol. 29, no. 6, pp. 415-423, Jun. 2018.

- [8] T. H. Jang, "Analysis of PCI cable effects in HEMP conducted disturbance," *The Journal of Korean Institute* of Electromagnetic Engineering and Science, vol. 24, no. 8, pp. 772-780, Aug. 2013.

- [9] Y. J. Kim, Y. B. Park, "Design and fabrication of a decoupler to conduct PCI verification test of a HEMP filter installed in a protection facility," *The Journal of Korean Institute of Electromagnetic Engineering and Science*, vol. 31, no. 6, pp. 535-541, Jun. 2020.

- [10] M. Magdowski, R. Vick, "Estimation of the mathematical parameters of double-exponential pulses using the nelder-mead algorithm," *IEEE Transactions on Electromagnetic Compatibility*, vol. 52, no. 4, pp. 1060-1062, Nov. 2010.

- [11] F. Qin, C. Mao, "Novel parameter estimation of double exponential pulses(EMP, UWB) by statistical Means," *IEEE Transactions on Electromagnetic Compatibility*, vol. 50, no. 1, pp. 97-100, Feb. 2008.

#### 문 재 식 [광운대학교/석・박사 통합과정]

#### https://orcid.org/0000-0002-5267-2752

2020년 2월: 광운대학교 전자통신공학과 (공학사)

2020년 3월~현재: 광운대학교 전자통신 공학과 석·박사 통합과정

[주 관심분야] System-Level EMC/EMI, EMP, 전도성 방해 내성 평가

### 송 익 환 [광운대학교/교수]

#### https://orcid.org/0000-0003-4176-6179

2004년 2월: 한국과학기술원 전기 및 전자 공학과 (공학사)

2006년 2월: 한국과학기술원 전기 및 전자 공학과 (공학석사)

2010년 2월: 한국과학기술원 전기 및 전자 공학과 (공학박사)

2011년~2013년: 삼성전자 글로벌기술센

터 책임연구워

2014년~현재: 광운대학교 전자통신공학과 부교수

[[주 관심분야] System-Level EMC/EMI. High-Speed Signal Integrity/Power Integrity, Electromagnetic Measurements Technologies

## 권 종 화 [한국전자통신연구원/책임연구원]

https://orcid.org/0000-0002-2132-7403

1994년 2월: 충남대학교 전자공학과 (공학 사)

1999년 2월: 충남대학교 전파공학과 (공학 석사)

2010년 2월: 연세대학교 전기전자공학과 (공학박사)

1999년 1월~현재: 한국전자통신연구원

통신미디어연구소 전파위성연구본부 전파환경감시연구실 책임연구원

[주 관심분야] 전자기장 해석, EMC/EMP 대책 및 측정·평가 기술, EMC/EMP 표준화 등