# 28-nm FD SOI CMOS 공정을 이용한 140 GHz 저잡음 증폭기 설계

# Design of a 140-GHz Low-Noise Amplifier Using 28-nm FD SOI CMOS Process

성 기 환·박 재 현·김 병 성

Ki-hwon Sung · Jae-hyun Park · Byung-sung Kim

요 약

본 논문은 28-nm CMOS FD SOI 공정을 이용해 D-band 저잡음 증폭기를 설계한 결과를 제시한다. 설계한 저잡음 증폭기는 3단 차동 공통소스 구조를 가지며, 트랜스포머를 사용해 각 단 및 입출력 임피던스 정합 회로를 구성하였다. 제작한 저잡음 증폭기는 139 GHz에서 최대이득 15.17 dB을 보이며, 3-dB 대역폭은 11 GHz이다. 제작한 칩의 면적은 패드를 포함해 0.255 mm²이며, 1.0 V 공급 전원에서 27 mW의 전력을 소비한다.

#### Abstract

This paper presents the design of a D-band, low-noise amplifier (LNA) employing a 28-nm, fully depleted silicon-on-insulator complementary metal-oxide-semiconductor technique. This designed LNA comprises a three-stage differential common-source amplifier, and impedance matching is achieved using a transformer. The fabricated LNA chip yields a peak gain of 15.17 dB at 139 GHz, with a 3-dB bandwidth of 11 GHz. The total area of the chip, including the pads, is 0.255 mm<sup>2</sup>, and the chip consumes 27 mW of DC power from a 1.0-V supply.

Key words: Low-Noise Amplifier, CMOS FD SOI Process, D-Band

# T. 서 론

수 mm 이내의 정밀도를 가지는 레이다나 수십 Gbps의 초고속 무선 데이터 통신을 위해 광대역 mm파 무선 시스템의 필요성이 대두되고 있다. 300 GHz 이하의 mm파 대역 중 140 GHz 대역은 비허가 대역으로 지정되어 있으며, 공기 중에서의 감쇠가 작아 무선통신 용도에 적합하다. 따라서, 최근 CMOS 공정의 발전으로 D-band에서 동작하는 송수신기에 관한 연구가 활발히 진행되고 있다<sup>[1],[2]</sup>.

본 논문에서는 D 밴드 수신기 설계의 일환으로 28-nm CMOS FD SOI 공정을 사용하여 140 GHz 대역 고이득 차동 저잡음 증폭기를 설계한 결과를 제시한다. Ⅱ장에서는 회로의 설계 내용에 대해 설명하고, Ⅲ장에서는 측정 및 시뮬레이션 결과를, 마지막으로 Ⅳ장에서는 결론을 제시한다.

# Ⅱ. 회로 설계

설계한 저잡음 증폭기는 3단 차동 공통소스 구조를 사

<sup>「</sup>이 연구는 삼성전자(Samsung Electronics Co., Ltd) 지원으로 수행한 연구 결과임.」

성균관대학교 정보통신대학(College of Information & Communication Engineering, Sungkyunkwan University

<sup>·</sup> Manuscript received March 20, 2020; Revised April 17, 2020; Accepted April 18, 2020. (ID No. 20200320-025)

<sup>·</sup> Corresponding Author: Byung-sung Kim (e-mail: bskimice@skku.edu)

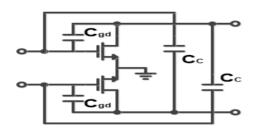

용하였다. 공통소스 구조는 밀리미터파 대에서 게이트와 드레인 사이에 존재하는 피드백 커패시터  $C_{gd}$ 에 의해 높은 이득과 안정성을 동시에 확보하기 어렵지만, 증폭기를 차동으로 설계하고, 커패시터  $C_c$ 를 교차 연결함으로써  $C_{gd}$ 를 상쇄시켜 차동 쌍의 최대가용이득과 안정성을 확보하였다.

그림 1은 단순화한 커페시턴스 중화 모델이고, 이를 토대로 최대 가용 이득(maximum available gain: MAG)과 안정지수 k값을 다음 식으로 구할 수 있다<sup>[3]</sup>.

$$MAG = \frac{\sqrt{w^{2}(C_{gd} - C_{C})^{2}R_{g}R_{d}}}{w\left|C_{gd} - C_{c}\right|}(k - \sqrt{k^{2} - 1}) \tag{1}$$

$$k = \frac{2 + w^2 (C_{gd} - C_C)^2 R_g R_d}{w \left| C_{gd} - C_c \right| R_g R_d \sqrt{w^2 (C_{gd} - C_C)^2 + g_m^2}}$$

(2)

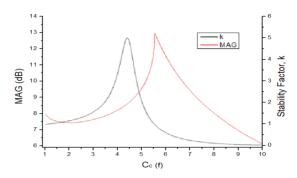

식 (1), (2)에서 볼 수 있듯이, MOSFET의  $C_{gd}$ 만을 고려한 경우, 중화 커페시턴스  $C_e$ 가  $C_{gd}$ 와 같을 때 중화된 차동 쌍은 가장 높은 이득과 안정성을 보인다. 그림 2는  $C_e$ 에 따른 MAG와 k의 변화를 보여준다. 따라서 커페시턴  $C_{gd}$ 와  $C_e$ 의 공정간 오차를 최소화하기 위해  $C_{gd}$ 와 공정간 오차가 유사한 MOS 커페시터를 중화 커페시턴스  $C_e$ 로 사용하였다.

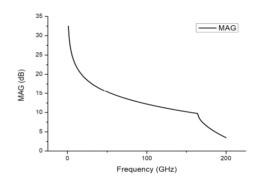

본 논문에서 사용된 MOSFET의 크기는 전력 소모를 고려하여 단일 가지 너비  $0.75~\mu$ m를 기준으로 FET의 폭을  $18~\mu$ m로 결정하였다. MOS 커패시터  $C_c$ 는 증폭기와 동일하게 단일 가지 너비  $0.75~\mu$ m를 기준으로 FET의 폭을  $13.5~\mu$ m로 결정하였다.  $18~\mu$ m 차동 증폭단을 캐패시터 중화하였을 때 단일 차동 증폭단의 MAG는 그림 3과 같으며,  $140~\mathrm{GHz}$ 에서는  $10.54~\mathrm{dB}$ 이다.

그림 1. 단순화한 커패시턴스 중화 모델

Fig. 1. Simplified capacitance neutralization model.

그림 2.  $C_2$ 에 따른 MAG와 k의 변화

Fig. 2. Variation of MAG and k with  $C_c$  at 140 GHz.

그림 3. 주파수에 따른 MAG의 변화

Fig. 3. Variation of MAG with frequency.

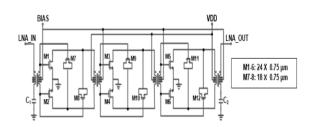

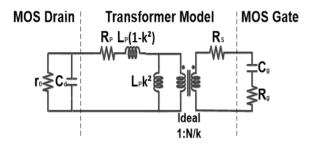

mm파 대역에서는 증폭기 한 단의 가용 이득이 낮기때문에 여러 단으로 증폭기를 설계하게 된다. 본 논문에서는 임피던스 정합 회로의 구조가 간단하고, 정합 회로에서의 손실이 적은 트랜스포머를 이용하여 그림 4와 같이 3단의 공통 소스 증폭기로 구성하였다. 그림 5는 각 단의 임피던스 정합을 위한 트랜스포머 모델을 나타낸 것이다. 트랜스포머는 1차 권선의 총 인덕턴스  $L_p$ , 자기 결합

그림 4. 설계한 저잡음 증폭기 회로도

Fig. 4. Low-noise amplifier schematic.

그림 5. 임피던스 매칭을 위한 트랜스포머 모델 Fig. 5. Transformer model for impedance matching.

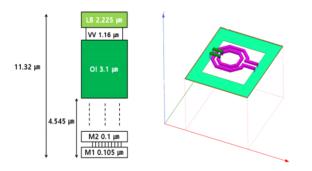

계수 k, 권선비 N으로 모델링할 수 있으며, 작은 면적에서 차동 증폭기의 각 단 임피던스 정합을 구현할 수 있는 장점이 있다. 트랜스포머의  $L_p$ , k, N을 결정할 수 있다<sup>4</sup>. 이렇게 결정된 트랜스포머 파라메터를 그림 6의 금속층 구성 정보와 같이 두꺼운 금속층인 OI 레이어를 이용하여 수평결합 구조로 설계하였다. 전자기 시뮬레이션에는 Ansoft 사의 HFSS를 사용하였다.

# Ⅲ. 측정 및 시뮬레이션 결과

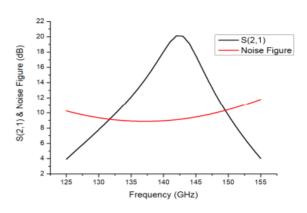

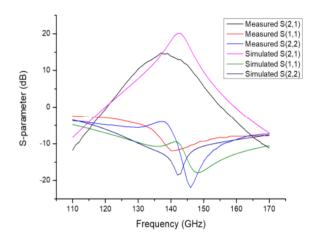

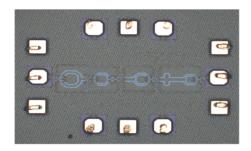

그림 9는 제안한 저잡음 증폭기를 28-nm CMOS FD SOI 공정으로 제작한 사진이다. Agilent사의 E8361A Power Network Analyzer를 이용하여 온 칩 프로빙으로 측정했다. 그림 7과 같이 잡음지수를 시뮬레이션하여 확인하였으며, 그림 8은 설계한 3단 차동 공통소스 저잡음 증

그림 6. 28-nm FD SOI 공정 금속층 정보와 수평 결합 구조 트랜스포머

Fig. 6. Metal layer information of 28-nm FD SOI process and horizontal coupled structure transformer.

그림 7. 시뮬레이션을 이용한 S(2,1)과 잡음지수 Fig. 7. Simulated S(2,1) and noise figure.

그림 8. 시뮬레이션과 측정 S-파라미터 결과 Fig. 8. Simulated and measured S-parameter result.

폭기의 시뮬레이션 값과 측정값을 비교한 결과이다. 설계한 증폭기는 139 GHz에서 15.17 dB의 최대이득과 11 GHz의 3-dB 대역폭을 보이며, 시뮬레이션 결과로 얻은 최소잡음 지수는 8.8 dB이다. 입력 발문의 positive /negative 위상차는 2°이다. 제작한 칩은 패드를 포함해 0.255 mm²의면적을 가지며, 1.0 V 공급 전압에서 27 mW의 직류 전력을 소모한다. 표 1에서는 설계한 증폭기의 성능을 기존의저잡음 증폭기들과 비교하였다. 시뮬레이션 대비 최대 이득의 저하 이유는 분석 중이며, 전자기 시뮬레이션의 한계로 인해 트랜스포머 하층의 메탈 더미 효과를 고려할수 없었는데, 실제 회로에서는 이 효과로 트랜스포머의 Q가 낮아진 것이 원인의 하나로 추정된다.

표 1. 저잡음 증폭기 성능 비교

Table 1. Performance comparison with other works.

| Ref.      | Process              | Туре                            | Peak gain (dB) | Peak gain<br>frequency<br>(GHz) | 3-dB BW (GHz) | Noise figure (dB) | P <sub>DC</sub> (mW) | Chip area (mm²) |

|-----------|----------------------|---------------------------------|----------------|---------------------------------|---------------|-------------------|----------------------|-----------------|

| [5]       | 65-nm CMOS           | 6-stage combined cascode and CS | 22.4           | 120                             | 16            | 11.4*             | 61                   | NA              |

| [6]       | 65-nm CMOS           | 8-stage CS                      | 14.4           | 126                             | 17            | 12                | 22.6                 | 1.9             |

| This work | 28-nm CMOS<br>FD SOI | 3-stage CS                      | 15.17          | 139                             | 11            | 8.8*              | 27                   | 0.255           |

<sup>\*</sup> Simulated value.

그림 9. 저잡음 증폭기 칩의 현미경 사진 Fig. 9. Chip micrograph of the LNA.

# Ⅳ. 결 론

본 논문에서는 28-nm CMOS FD SOI CMOS 공정을 사용하여 D-band 저잡음 증폭기를 설계하였다. 제작한 저잡음 증폭기는 139 GHz에서 최대이득 15.17 dB를 가지며, 11 GHz의 3-dB 대역폭을 가진다. 향후 레이다 및 고속 데이터 통신 수신기에 활용할 수 있을 것으로 기대된다.

# References

[1] A. Visweswaran, K. Vaesen, S. Sinha, I. Ocket, M. Glassee, and C. Desset, et al., "9.4A 145 GHz FMCW-radar transceiver in 28 nm CMOS," in 2019 IEEE International Solid-State Circuits Conference (ISSCC), San

Francisco, CA, Feb. 2019, pp. 168-170.

- [2] J. Elkind, E. Socher, "A 154~165 GHz LNA and receiver in CMOS 65 nm technology," in 2016 11th European Microwave Integrated Circuits Conference (EuMIC), London, Oct. 2016, pp. 393-396.

- [3] H. Asada, K. Matsushita, K. Bunsen, K. Okada, and A. Mastsuzawa, "A 60 GHz CMOS power amplifier using capacitive cross-coupling neutralization with 16% PAE," in 2011 41st European Microwave Conference, Manchester, Oct. 2011, pp. 1115-1118.

- [4] J. R. Long, "Monolithic transformers for silicon RF IC design," *IEEE Journal of Solid-State Circuits*, vol. 35, no. 9, pp. 1368-1382, Sep. 2000.

- [5] C. J. Lee, T. H. Jang, "A CMOS D-band low noise amplifier with 22.4 dB gain and a 3 dB bandwidth of 16 GHz for wireless chip to chip communication," 2017 PIERS, Nov. 2017.

- [6] K. Katayama, K. Takano, S. Amakawa, T. Yoshida, and M. Fujishima, "14.4-dB CMOS D-band low-noise amplifier with 22.6-mW power consumption utilizing biasoptimization technique," in 2016 IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), Taipei, Aug. 2016, pp. 1-3, 2016.