# 65 nm CMOS 공정을 이용한 저면적 30~46 GHz 광대역 증폭기 30~46 GHz Wideband Amplifier Using 65 nm CMOS

신 미 애ㆍ서 문 교

Miae Shin · Munkyo Seo

요 약

본 논문에서는 칩 면적을 최소화한 65 nm CMOS 기반 30~46 GHz 대역 광대역 증폭기 회로의 설계 및 측정결과에 대하여 기술하였다. 전체 증폭기의 칩 면적을 줄이기 위해 결합 인덕터를 이용한 임피던스 정합회로를 사용하였다. 제작된 광대역 증폭기 회로는 9.3 dB 최대 이득, 16 GHz의 3 dB 대역폭 및 42 % 비대역폭 등의 측정 결과를 보였다. 입출력반사 손실은 각각 35.8~46.0 GHz 대역과 28.6~37.8 GHz 대역에서 10 dB 이상이다. 공급 전압은 1.2 V이며, 소비 전력은 42 mW이다. 3 dB 대역폭 내에서의 군 지연 변화는 19.1 ps이며, 패드를 제외한 칩 면적은 0.09 mm²이다.

### **Abstract**

This paper presents a miniaturized 65 nm CMOS 30~46 GHz wideband amplifier. To minimize the chip area, coupled inductors are used in the matching networks. The measurement shows that the fabricated amplifier exhibits 9.3 dB of peak gain, 16 GHz of 3 dB bandwidth, and 42 % fractional bandwidth. The measured input and output return losses were more than 10 dB at 35.8~46.0 GHz and 28.6~37.8 GHz, respectively. The chip consumes 42 mW at 1.2 V. The measured group delay variation is 19.1 ps within the 3 dB bandwidth and the chip size excluding the pads is 0.09 mm<sup>2</sup>.

Key words: Wideband Amplifier, Fractional Bandwidth, Coupled Inductor, Group Delay, Q-Band

## T. 서 론

최근 무선통신 기술의 발달 및 이용자 증가에 따라 소비되는 모바일 데이터 트래픽이 기하급수적으로 증가하고 있고<sup>[1]</sup>, 이에 상대적으로 넓은 대역폭 확보 및 고속의데이터 송수신이 가능한 밀리미터파(millimeter wave) 대역 광대역 통신 회로의 구현에 관한 연구가 급증하고 있다<sup>[2]</sup>. 특히, 38 GHz 대역은 5세대 이동통신(5G)과 관련하여 기기 간 통신(device to device), 자동차 애플리케이션 (automotive applications) 등의 상업용 목적으로 연구가 활

발히 진행되고 있다<sup>[3],[4]</sup>.

광대역 증폭기의 칩 면적은 일반적으로 다수의 인덕터 사용으로 인하여 큰 경향이 있는데, 이는 향후 다채널 유무선 통신 시스템 구현에 걸림돌로 작용할 수 있다. 본 논문에서는 칩 면적을 최소화한 밀리미터파 대역 65 nm CMOS 광대역 증폭기의 설계 및 측정 결과에 대해 기술한다. Ⅱ장에서 기존 밀리미터파 대역 광대역 증폭기 결과를 요약하였다. Ⅲ장에서는 30~46 GHz 대역에서 동작하는 본 논문의 광대역 증폭기의 설계에 대하여 서술하였고, Ⅳ장에서 측정 결과를 정리했다.

<sup>「</sup>이 논문은 2016년도 정부(교육부)의 재원으로 한국연구재단의 지원을 받아 수행된 기초연구사업임(No.2016R1D1A1B03934114).」

성균관대학교 전자전기컴퓨터공학부(Department of Electronic and Computer Engineering, Sungkyunkwan University)

<sup>·</sup> Manuscript received April 3, 2018; Revised April 17, 2018; Accepted May 3, 2018. (ID No. 20180403-045)

<sup>·</sup> Corresponding Author: Munkyo Seo (e-mail: mkseo@skku.edu)

### Ⅱ. 기존 밀리미터파 대역 광대역 CMOS 증폭기

5세대 이동통신 등의 응용을 위하여 최근 CMOS 공정을 이용한 다양한 구조의 밀리미터파 대역 광대역 증폭기들이 발표되었다. 충분한 증폭기 이득을 얻기 위하여 광대역 증폭기는 일반적으로 다단(multi-stage) 구조로 설계된다. 증폭기의 입출력 및 중간단(inter-stage) 임피던스정합을 위해서 다수의 인덕터가 필요한데, 이로 인하여광대역 증폭기의 칩 면적은 상대적으로 큰 경향이 있다. 참고문헌 [5]에서는 증폭기 칩의 소형화를 위해 변압기(transformer)를 사용하였고, 참고문헌 [6]에서는 증폭기의광대역화와 소형화를 위해 노턴 변환(Norton transform)을이용하였다. 참고문헌 [7]에서는 피킹 네트워크(peaking network)를 이용하여 광대역 증폭기를 구현하였다.

## Ⅲ. 광대역 증폭기 설계

광대역 증폭기의 구현을 위해서는 분산(distributed) 구조 또는 피드백(feedback) 구조의 사용이 가능하다. 분산 증폭기는 일반적으로 칩 면적이 큰 경향이 있고 피드백 증폭기는 일반적인 능동 소자의 전력 이득이 밀리미터파 대역에서 상대적으로 낮은 관계로 효율적인 구현이 어렵다. 본 논문에서는 밀리미터파 대역에서 상대적으로 고 이득의 구현이 용이한 캐스코드(cascode) 구조 기반 다단 증폭기를 설계하였고, 칩 면적의 최소화를 위하여 결합 인덕터(coupled inductor)를 이용하여 임피던스 정합회로를 구현하였다.

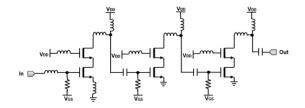

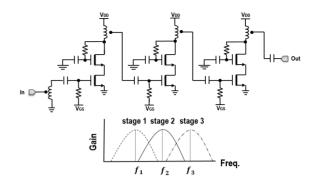

그림 1은 캐스코드 구조에 기반을 둔 기존 광대역 증폭기 회로이다<sup>18</sup>(광대역화를 위해 게이트에 유도성 피드백 적용). 그림 2는 본 논문에서 설계한 광대역 증폭기 회로이다. 각 임피던스 정합 단의 중심 주파수를 조금씩 달리

그림 1. 기존의 캐스코드 기반 광대역 증폭기 회로도<sup>[8]</sup> Fig. 1. Schematic of conventional cascode-based wideband amplifier<sup>[8]</sup>.

그림 2. 본 논문의 광대역 증폭기 회로도 Fig. 2. Schematic of the wideband amplifier in this work.

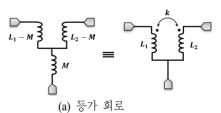

하여 전체적인 증폭기 이득이 광대역에서 평탄한 특성을 갖게끔 설계하였고, 결합 인덕터를 사용하여 임피던스 정합회로를 구현하였다. 이로 인하여, 기존 회로에서 인접한 두 개의 인덕터를 하나의 결합 인덕터로 대체할 수 있으므로 전체 증폭기의 소형화 구현이 가능하다. 그림 3에 결합 인덕터의 등가회로 및 레이아웃을 나타내었다. 그림 3(a)의 왼쪽은 세 개의 단독 인덕터 및 상호 인덕턴스 M을 이용한 등가회로이고, 그림 3(b)의 오른쪽은 하나의 결합 인덕터 및 결합 상수 k를 이용한 등가회로인데, 이 두모델은 서로 동등하며,  $k=M/\sqrt{L_1L_2}$ 의 관계가 있다<sup>19</sup>. 그림 3(a) 왼쪽의 단독 인덕터 등가회로를 이용하여 회로

(a) Equivalent circuits

(b) 레이아웃 (b) Layout

그림 3. 결합 인덕터

Fig. 3. Coupled inductor.

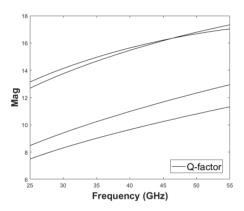

를 설계하고, 실제 레이아웃은 그림 3(a)의 오른쪽 등가회로에 따라서 상호 인덕턴스를 갖는 그림 3(b)의 형태로구현하였다. 그림 4에 구현된 결합 인덕터의 *Q*-factor를나타내었다. 각 단의 임피던스 정합회로는 전체 증폭기의최대 이득, 대역폭 및 군 지연(group delay) 변화 특성을고려하여 설계하였다.

# Ⅳ. 측정 결과

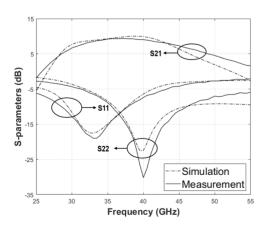

설계된 광대역 증폭기는 65 nm CMOS 공정을 이용하여 제작하였으며, 벡터 회로망 분석기(vector network analyzer) 를 이용하여 2 단자 산란 계수(scattering parameter: *S*-parameter)를 측정하였다. 그림 5에서 보듯이, 측정된 3 dB 대

그림 4. 결합 인덕터의 Q-factor

Fig. 4. Q-factors of coupled inductors.

그림 5. 광대역 증폭기의 측정된 산란계수

Fig. 5. Measured S-parameters of the wideband amplifier.

역폭은 29.8~46.6 GHz로 42.1 %의 비대역폭을 가지며, 최대 이득은 9.3 dB로 측정되었다. 입력 반사 손실은 36.4~46 GHz 대역에서, 출력 반사 손실은 29.6~37.9 GHz 대역에서 10 dB 이상이다. 비대역폭 *B*는 다음 식 (1)의 정의를 이용하였다.

$$B = \frac{f_{3dB_{high}} - f_{3dB_{low}}}{f_{3dB_{high}} + f_{3dB_{low}}} \times 2 \tag{1}$$

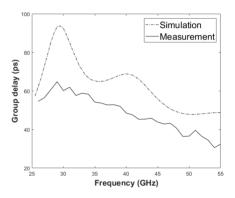

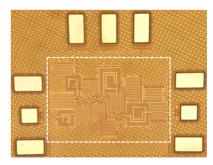

그림 6에 측정된 군 지연 변화를 나타내었다. 증폭기 3 dB 대역폭 내에서의 군 지연 변화는 19.1 ps로, 이는 20 Gbps의 전송을 가능하게 한다<sup>[10]</sup>. 그림 7에 제작된 광대역 증폭기의 칩 사진을 나타내었다. 패드를 제외한 증폭기회로 자체의 칩 면적은 0.09 mm<sup>2</sup>이며, 패드를 포함한 전

그림 6. 광대역 증폭기의 측정된 군 지연 변화

Fig. 6. Measured group delay variations of the wideband amplifier.

그림 7. 광대역 증폭기 칩 사진(패드를 제외한 칩 크기: 0.37×0.24 mm²)

Fig. 7. Wideband amplifier chip photograph(chip size excluding pads: 0.37×0.24 mm²).

| 丑 1.  | 기존    | 광대역      | 증폭기       | 연구    | 결과와.    | 의 비교        |

|-------|-------|----------|-----------|-------|---------|-------------|

| Table | 1. Co | ompariso | on of rec | ent w | ideband | amplifiers. |

|                                      | Ref. [5] | Ref. [6] | Ref. [7] | This work |

|--------------------------------------|----------|----------|----------|-----------|

| Process                              | 90 nm    | 40 nm    | 90 nm    | 65 nm     |

| Process                              | CMOS     | CMOS     | CMOS     | CMOS      |

| Frequency [GHz]                      | 29~44    | 24~54    | 30~50    | 30~46     |

| Peak gain [dB]                       | 13.8     | 7        | 23       | 9.3       |

| 3 dB fractional BW [%]               | 41.0     | 76.9     | 50.0     | 42.1      |

| Group delay variation [ps]           | N/A      | 35.0     | N/A      | 19.1      |

| Power consumption [mW]               | 18       | 34       | 20.4     | 42        |

| *Chip area [mm²]<br>(Excluding pads) | 0.23     | 0.15     | 0.22     | 0.09      |

체 칩 면적은 0.27 mm<sup>2</sup>이다. 제작된 증폭기는 1.2 V의 단 일전원으로 동작하며, 42 mW의 전력을 소모한다.

본 논문의 광대역 증폭기를 기존의 연구와 비교하여 표 1에 정리하였다. 본 논문의 광대역 증폭기의 비대역폭은 42 %로 기존 결과와 유사한 수준이고, 패드를 제외한 회로 자체의 면적은 비교 논문 대비 최소이다. 본 증폭기의 비교적 낮은 최대 이득은 Ⅲ장에서 언급하였듯이 광대역 구현을 위한 단 간의 의도적인 임피던스 부정합에 기인한 것으로 파악된다.

## Ⅴ. 결 론

본 논문에서는 65 nm CMOS 공정을 이용한 30~46 GHz 대역 광대역 증폭기의 설계 및 측정 결과를 기술하였다. 측정된 비대역폭은 42 %이고, 패드를 제외한 칩 면적이 0.09 mm²로 기존 광대역 증폭기 대비 상대적으로 작으므로, 초고속 다채널 유무선 통신 시스템의 구현에 유리하다. 본 증폭기의 입출력 반사손실은 비교적 협대역 특성을 보이고 있어서 이의 광대역화에 관한 후속 연구를 진행할 예정이다.

### References

[1] 장재득, 김철호, 이희동, 장승현, 강병수, 박봉혁 외, "밀리미터파 기반 5세대 이동통신 RF 기술/ 시장동향," 전자통신동향분석, 31(5), pp. 41-50, 2016년 10월.

- [2] J. L. Kuo, Z. M. Tsai, K. Y. Lin, and H. Wang, "A 50 to 70 GHz power amplifier using 90 nm CMOS technology," *IEEE Microwave and Wireless Components Letters*, vol. 19, no. 1, pp. 45-47, Jan. 2009.

- [3] J. Kim, A. F. Molisch, "Quality-aware millimeter-wave device-to-device multi-hop routing for 5G cellular networks," in 2014 IEEE International Conference on Communications(ICC), Sydney, NSW, Jun. 2014, pp. 5251-5256.

- [4] J. Udomoto, T. Matsuzuka, S. Chaki, K. Kanaya, T. Katoh, and Y. Notani, et al., "A 38/77 GHz MMIC transmitter chip set for automotive applications," in *IEEE MTT-S International Microwave Symposium Digest*, Philadelphia, PA, Jun. 2003, vol. 3, pp. 2229-2232.

- [5] H. C. Yeh, C. C. Chiong, S. Aloui, and H. Wang, "Analysis and design of millimeter-wave low-voltage CMOS cascode LNA with magnetic coupled technique," *IEEE Microwave Theory and Techniques*, vol. 60, no. 12, pp. 4066-4079, Dec. 2012.

- [6] V. Bhagavatula, M. Taghivand, and J. C. Rudell, "A compact 77 % fractional bandwidth CMOS band-pass distributed amplifier with mirror symmetric Norton transforms," *IEEE Journal of Solid-State Circuits*, vol. 50, no. 5, pp. 1085-1093, May 2015.

- [7] G. L. Yang, F. Liu, A. Muhammad, and Z. Wang, "30~ 50 GHz high-gain CMOS UWB LNA," *Electronics Letters*, vol. 49, no. 25, pp. 1622-1623, Dec. 2013.

- [8] H. H. Hsieh, P. Y. Wu, C. P. Jou, F. L. Hsueh, and G. W. Huang, "60 GHz high-gain low-noise amplifiers with a common-gate inductive feedback in 65 nm CMOS," in 2011 IEEE Radio Frequency Integrated Circuits Symposium, Baltimore, MD, 2011, pp. 1-4.

- [9] C. K. Alexander, Matthew N. O. Sadiku, Fundamentals of Electric Circuits, Mcgraw-Hill, 2013.

- [10] A. Azizzadeh, L. Mohammadi, "Degradation of BER by group delay in digital phase modulation," in 2008 Fourth Advanced International Conference on Telecommunications, Athens, Jun. 2008, pp. 350-354.