# 77~81 GHz 근거리 레이다 시스템 IQ 수신단을 위한 LO 입력단의 설계 및 분석

# Design and Analysis of an LO Chain for an IQ Receiver in a 77~81 GHz Short-Range Radar System

송재혁 $^1$  · 임정택 $^2$  · 이재은 $^3$  · 손정택 $^4$  · 김준형 $^5$  · 백민석 $^6$  · 이은규 $^7$  · 김기진 $^8$ \* · 김철영 $^9$

Jae-Hyeok Song<sup>1</sup> · Jeong-Taek Lim<sup>2</sup> · Jae-Eun Lee<sup>3</sup> · Jeong-Taek Son<sup>4</sup> · Joon-Hyung Kim<sup>5</sup> · Min-Seok Baek<sup>6</sup> · Eun-Gyu Lee<sup>7</sup> · Ki Jin KIm<sup>8</sup>\* · Choul-Young Kim<sup>9</sup>

#### 유 약

본 논문은 CMOS 65 nm bulk 공정으로 설계된 LO 입력단 설계 및 분석에 관한 내용이다. LO 입력단은 77~81 GHz 대역의 근거리 레이더 IQ 믹서 구동을 위해 제작되었다. LO 입력단은 IQ 신호 생성을 위한 다상 필터(PPF)와 PPF의 손실을 보상하고, 적절한 출력 전력을 위한 구동 증폭기와 3-비트 7-dB 감쇄기로 구성하였다. 측정 결과 77~81 GHz 대역에서 최대 이득 8 dB이며, IQ 출력간 이득과 위상 차이는 각각 0.5 dB, 74°이다. LO 입력단은 1 V 전압에서 74 mW의 전력을 소모하며, 제작된 칩의 크기는 RF 및 DC 패드를 포함하여 1.027 × 0.45 mm²이다.

### Abstract

This paper presents the design and analysis of an LO chain implemented using the CMOS 65 nm bulk process. The LO chain was fabricated for driving the short-range radar IQ mixer in the  $77 \sim 81$  GHz band. The LO chain comprised a poly phase filter (PPF), driver amplifiers to compensate for PPF losses, and a 3-bit 7-dB attenuator to ensure the appropriate power conditions. Measurement results indicated that the maximum gain within the target band was 8 dB, and the gain and phase difference between the IQ outputs were 0.5 dB and  $74^{\circ}$ , respectively. The LO chain consumed 74 mW of power at 1 V, and the size of the fabricated chip was  $1.027 \times 0.45$  mm², including RF and DC pads.

Key words: O Chain, Poly-Phase Filter (PPF), Radar, W-Band

This work was supported by Institute for Information & communications Technology Promotion (IITP) grant funded by the Korea government (MSIP) [2021-0-00151, A Development of W band Chirp Radar RFIC for Level Sensor] and by the National Research Foundation of Korea (NRF) grant funded by the Korea government (MSIT) (No.NRF-2021R1A4A1032580).

충남대학교 전자공학과(Department of Electronic Engineering, Chungnam National University)

<sup>\*</sup>한국전자기술연구원(Korea Electronics Technology Institute)

<sup>1:</sup> 박사과정(https://orcid.org/0000-0003-3736-2753), 2: 박사과정(https://orcid.org/0000-0002-2698-6942),

<sup>3:</sup> 석·박사통합과정(https://orcid.org/0000-0001-6616-6503), 4: 석·박사통합과정(https://orcid.org/0000-0003-4794-5813),

<sup>5:</sup> 석·박사통합과정(https://orcid.org/0000-0002-6873-9034), 6: 석·박사통합과정(https://orcid.org/0000-0002-3651-4498),

<sup>7:</sup> 박사후연구원(https://orcid.org/0000-0002-3835-2226), 8: 책임연구원(https://orcid.org/0000-0002-5273-4167),

<sup>9:</sup> 교수(https://orcid.org/0000-0002-5532-7399)

<sup>·</sup> Manuscript received October 28, 2023; Revised November 2, 2023; Accepted December 21, 2023. (ID No. 20231028-091)

<sup>·</sup> Corresponding Author: Choul-Young Kim (e-mail: cykim@cnu.ac.kr)

## T. 서 론

최근 CMOS 공정의 발전으로 저비용으로 높은 집적도와 성능을 갖는 W 대역 RFIC의 개발이 가능해졌다<sup>[1]</sup>. 특히, 77~81 GHz 대역에서 4 GHz의 넓은 대역폭과 높은 분해능의 장점을 활용한 근거리 차량용 레이다를 위한 RFIC의 연구가 활발하다<sup>[2],[3]</sup>. IQ 레이다 시스템을 구동하기 위해서는 IQ 신호를 생성하기 위한 다상 필터(poly phase filter, PPF)를 포함하는 LO 입력단이 필요하다. LO 입력단은 위상동기회로 (phase locked loop, PLL)와 주파수 체배기를 통해 입력된 신호를 90° 차이의 IQ 신호로생성하고, 믹서를 구동하기 위한 적절한 전력으로 유지및 증폭하는 역할을 한다. 이때, 소비 전력을 최소화하는 것도 중요한 고려 사항이다.

본 논문은 77~81 GHz 근거리 레이다 시스템을 위한 LO 입력단을 CMOS 65nm bulk 공정을 사용해 설계하고, 측정 결과와 분석을 제시한다. 제작된 LO 입력단은 PPF 의 손실을 보상하고, 최적의 믹서 구동을 위한 전력으로 증폭 및 유지하기 위해 제작되었다.

#### Ⅱ. LO 입력단 설계

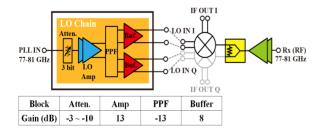

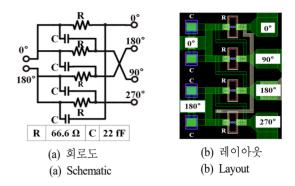

그림 1은 레이다 시스템의 IQ 수신단 예시와 설계한 LO 입력단의 블록도이다. IQ 믹서의 구동을 위해 필요한 LO 전력은 약 0 dBm 정도이며<sup>[4],[5]</sup>, 수동형 주파수 체배기의 경우 출력 전력은 0 dBm 이하이다<sup>[6]</sup>. 일반적인 RC-PPF는 높은 삽입 손실 때문에, 주파수 체배기와 믹서 사이에 신호 증폭과 PPF의 손실을 보상하기 위한 구동 증폭기가 필요하다. IQ 신호 생성을 위해 그림 2와 같이 1차 RC-PPF를 설계하였다. 시뮬레이션된 RC-PPF의 삽입

그림 1. LO 입력단과 IQ 수신단 블록도

Fig. 1. Block diagram of LO chain and IQ receiver.

그림 2. 다상 필터 Fig. 2. Poly phase filter.

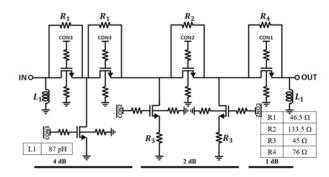

그림 3. 감쇄기 회로도

Fig. 3. Schematic of attenuator.

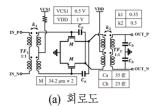

손실이 약 −13 dB 였고, 이를 보상하기 위해 2단의 LO 증폭기를 사용하였다<sup>[7]</sup>. 그림 3의 3-비트의 7-dB 감쇄기 는 믹서와 주파수 체배기의 동작 조건에 따라 LO 입력단 의 이득을 조절하기 위해 추가하였으며, IO 신호 균형을 위해 단일 신호 단자인 LO 증폭기 앞쪽에 배치하였다. 4-dB와 2-dB 감쇄기는 광대역 특성을 위해 각 T 형, π 형 을 사용하였다<sup>[8]</sup>. 상대적으로 낮은 감쇄인 1-dB 감쇄기는 저항 스위치형으로도 시뮬레이션에서는 충분한 성능을 보여 간단한 구조로 채택하였다. 50 Ω 정합을 위해 입출 력 단자에 병렬 인덕터  $(L_1)$ 를 추가하였다. PPF의 출력을 믹서로 잘 전달하기 위해 그림 4의 LO 버퍼를 설계하였 다. 각 IQ 단자의 차동 신호 전달을 위해 완전 차동 증폭 기로 설계하고, 중성화 커패시터를 사용하여 이득과 안정 성을 높였다. 각 회로는 소자의 상호 연결을 위한 금속 선 로에서 발생하는 기생 소자의 영향을 반영하기 위해 전 자기장 시뮬레이션을 하였다.

- (a) Schematic

- TF, TF<sub>2</sub> OUT

- (b) 레이아웃

- (b) Layout

그림 4. LO 버퍼 Fig. 4. LO buffer.

# Ⅲ. 측정 결과 및 분석

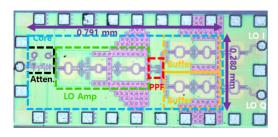

그림 5는 설계한 LO 입력단의 측정을 위해 제작된 측정용 칩의 현미경사진이다. DC 패드는 측정용 PCB에 와이어 본딩으로 인가하였으며, GSG 프로브 팁을 이용하여온 웨이퍼 측정하였다. 각 IQ 신호 출력에 대한 차동 신호 측정이 불가능하여, 각각 한 단자 측정을 위해 정합 회로를 추가하여 제작하였다. 측정용 정합 회로를 제외한 LO 입력단의 크기는 0.791×0.28 mm²이다.

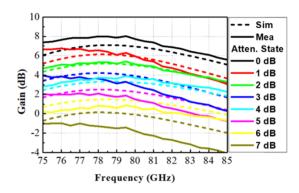

그림 6은 감쇄기의 동작에 따른 LO 입력단의 이득을 나타낸다. 77~81 GHz에서 감쇄가 없을 때, 최대 이득은 8 dB이다. 특정 감쇄기의 동작 상태에서 시뮬레이션과 차이를 보였고, 대체로 1-dB 감쇄기가 동작할 때 차이가 두드러졌다. 다른 감쇄기 비트의 구조와 달리 단순 저항 네

그림 5. 제작된 LO 입력단의 현미경사진 Fig. 5. Microphotograhy of LO chain.

그림 6. 감쇄기 동작에 따른 LO 입력단의 이득 Fig. 6. Gain of LO chain according to attenuator operation.

트워크에 의한 감쇄가 이루어진 것이 오차의 원인으로 보인다.

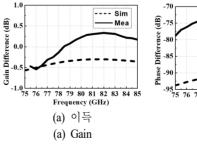

그림 7은 IQ 출력에 따른 이득과 위상 차이를 나타낸다. 동일한 입력 조건에서 각 IQ 출력을 각각 측정하였으며, I를 기준으로 Q의 상대값을 나타내었다. 77~81 GHz에서 IQ 경로의 이득 차이는 0.5 dB 이내이며, 위상 차이는 약 74°이다. IQ 경로의 이득 차이는 시뮬레이션과 거의 유사하나 위상 차이는 목표 위상 차이인 90°와 오차가 컸다. 원인으로는 PPF의 RC 사이를 연결하는 금속 선로의 비대칭 구조와 단일 PPF의 공정변화 취약성으로 보인다. 그림 2 (b)의 레이아웃에서 270° 신호의 출력 경로의RC 연결을 위한 선로는 다른 선로와 차이가 있으며, 이로인해 기생 소자의 값의 영향이 다르게 작용한 것으로 보인다. 또한, 시뮬레이션에서 RC 소자값에 의한 출력 위상의 변화가 민감하였다. 그림 7 (b)의 위상 그래프 개형에따라 측정값은 목표 대역보다 높은 주파수 대역의 위상으로 이동한 것으로 보이며, 공정변화에 의한 영향으로

그림 7. IQ 출력 차이

Fig. 7. IQ ouput difference.

보인다. 또한, 사용한 공정은 30 GHz까지 PDK(process design kit)의 모델링을 보장하여, W 대역의 높은 주파수 대역에서의 소자값의 부정확함 또한 원인으로 작용했다. 이러한 오차를 줄이기 위해서는 다단 PPF를 사용하여 넓은 주파수 범위에서 일정한 IQ 위상 차이를 갖도록 하는 것이 적절할 것으로 보인다. 다단 RC-PPF 사용에 따라 면적과 경로 손실이 증가한다. 그러나, 늘어난 면적은 다른 블록에 비해 전체 면적에 영향이 적고, 증가한 손실은 배수가 아닌 한 단 증가에 따라 약 6-dB 정도였다. LO 입력단은 1 V 전원에서 총 74 mW의 전력을 소모한다.

# Ⅳ. 결 론

본 논문에서는 IQ 레이다 수신단에 적용 가능한 LO 입력단을 CMOS 65nm bulk 공정을 사용하여 설계 및 제작하였다. 제작된 LO 입력단은 77~81 GHz로 체배된 주파수를 IQ 신호로 직접 변환하기 위해 다상 필터 (PPF)와 IQ 믹서 구동에 필요한 적절한 전력 공급을 위한 증폭기및 감쇄기로 구성된다. 표 1은 동일 대역 IQ 생성 회로와의 성능을 비교한 것이다. 측정 및 분석을 통해 각 회로의 개선 방향에 대해 제시하였다.

#### References

[1] J. Zhang, S. S. Ahmed and A. Arbabian, "A W-band spillover-tolerant mixer-first receiver for FMCW radars," in 2023 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), San Diego, CA, 2023, pp. 241-244.

표 1. I/Q 생성 회로 성능 비교 Table 1. Comparison with other works.

| Ref.                   | This work | Ref. [1] | Ref. [3] |

|------------------------|-----------|----------|----------|

| Tech.                  | 65 nm     | 40 nm    | 28 nm    |

|                        | CMOS      | CMOS     | CMOS     |

| Topology               | RC-PPF    | Hybird   | CML      |

| Freq. [GHz]            | 77-81     | 80-90    | 89-93    |

| I/Q Amp. Diff. [dB]    | < 0.5     | N/A      | N/A      |

| I/Q Phase Diff. [Deg.] | 74        | 90       | 90       |

| Pdc [mW]               | 74        | 28       | N/A      |

- [2] D. Pan, Z. Duan, B. Wu, Y. Wang, D. Huang, and Y. Wang, et al., "A digitally controlled CMOS Receiver with -14 dBm P1dB for 77 GHz automotive radar," in 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 2019, pp. 1-4.

- [3] R. Huang, C. W. Chiang, C. J. Liang, Y. Kim, Y. C. Kuan, and M. C. F. Chang, et al., "A W-band 4-GHz BW multiuser interference-tolerant radar with 28-nm CMOS front ends," *IEEE Solid State Curcuits Letters*, vol. 3, pp. 414-417, 2020.

- [4] H. Duan, J. Chen, M. Wang, H. Wei, Q. Zhang and H. Quan, "High linearity wide band passive mixer for Kuband applications in a 180nm CMOS technology," in 2022 7th International Conference on Integrated Circuits and Microsystems(ICICM), Xi'an, China, 2022, pp. 565-569.

- [5] J. H Song, J. T. Lim, J. E. Lee, J. T. Son, J. H. Kim, and M. S. Baek, et al., "Design of down-conversion Q-boosting mixer for W-band radar systems," *The Journal of Korean Institute of Electromagnetic Engineering and Science*, vol. 34, no. 11, pp. 852-855, Nov. 2023.

- [6] J. T. Oh, J. J. Jang, C. Y. Kim and S. C. Hong, "A W-band high-efficiency CMOS differential current-reused frequency doubler," *IEEE Microwave and Wireless Components Letters*, vol. 25, no. 5, pp. 307-309, May 2015.

- [7] J. S. Park, J. H. Song, J. T. Lim, J. E. Lee, J. T. Son, J. H. Kim, et al., "Design of drive amplifier for W-band RFIC," *The Journal of Korean Institute of Electromagnetic Engineering and Science*, vol. 34, no. 11, pp. 848-851, Nov. 2023.

- [8] B. H. Ku and S. C. Hong, "6-bit CMOS digital attenuators with low phase variations for X-band phased-array systems," *IEEE Transactions on Microwave Theory and Techniques*, vol. 58, no. 7, pp. 1651-1663, Jul. 2010.